00 - Sigrity X Topology Workbench Overview

Purpose

This RAK demonstrates how to use Topology Workbench (TopWb) in the SI exploration workflow to create and extract topologies for the critical nets in PCB and derive Electrical Constraint Set (ECSet) by using topologies to optimize the design.

This document has the step-by-step instructions on exploring the Sigrity X Topology Workbench canvas, creating a topology from scratch, doing pre-layout extraction and post-layout routed interconnect extraction, and updating the ECSet by using Constraint Manager.

Audience

This document is intended for Signal Integrity and PCB layout design engineers who want to run a detailed design-oriented analysis of prerouted and postrouted boards.

Terms

| TopWb | Topology Workbench |

| TopXp | Topology Explorer |

| SigXplorer | Signal Explorer |

| ECSet | Electrical Constraint Set |

| PDN | Power Distribution Network |

| CM | Constraint Manager |

| MCP | Constraint Manager |

Directory Structure

Click here to access the files below to run the labs*.

- prelayout_Module1.brd – physical layout file to be used in Module 2

- postlayout_Module1.brd – physical layout file to be used in Module 3

*These files are on a Cadence Online Support (COS) page. A COS account is needed to access the files.

Overview

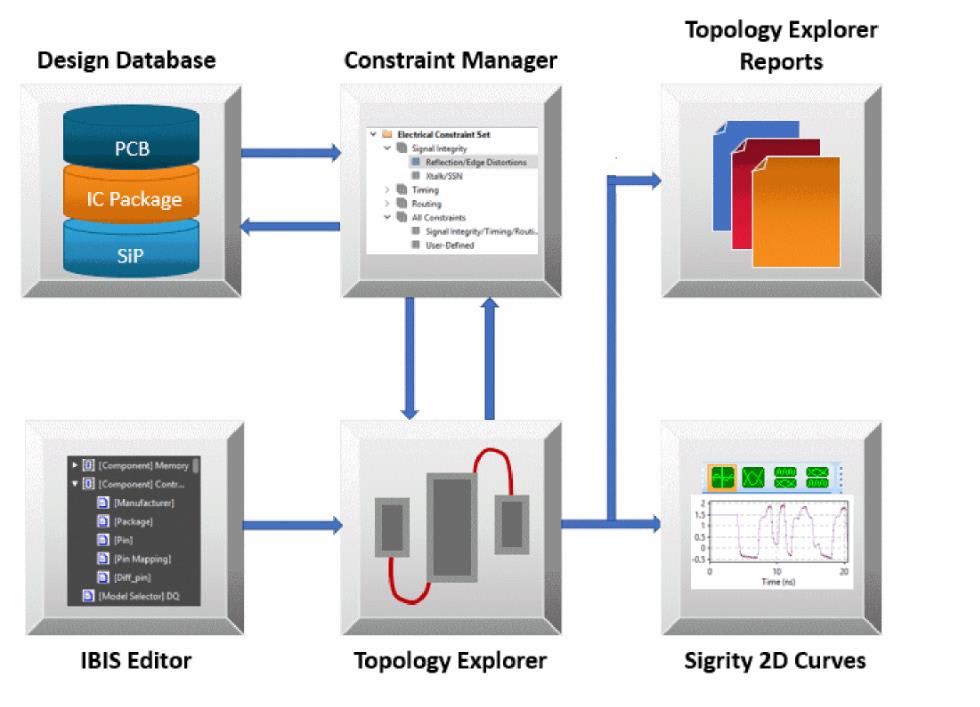

Sigrity X Topology Workbench is an advanced SPICE-based simulation and analysis environment that enables exploring, identifying, and solving the adverse analog effects of high-speed digital systems. It is the next-generation topology environment that replaces both Sigrity X System Explorer and Cadence SigXplorer tools from Cadence System Analysis 24.1 (SPB 24.1) and earlier releases.

You can optimally use Sigrity X Topology Workbench along with the other tools for Exploration, Preroute Analysis, and Postroute Verification.

The easy-to-use interface of Sigrity X Topology Workbench lets you visually do the following

- Construct or extract interconnect topologies for signals or PDNs.

- Run simulations or sweep multiple scenarios with a series of simulations.

- Generate reports to review results.

- Capture constraints to be passed back to the Allegro PCB/package layout environment.

This RAK guides you to first create a new topology from scratch in Sigrity X Topology Workbench to run an extensive ‘What-If’ analysis. Then, you will extract a topology by using CM and use that to create a constraint set to update the layout.

View the next document: 01 - Exploring the Workbench Canvas With Topology Creation

If you have any questions or comments about the OrCAD X platform, click on the link below.

Contact Us