Controlled Impedance Design Guide

Key Takeaways

-

Effective controlled impedance design involves managing factors such as trace width, copper thickness, dielectric thickness, and stack-up configuration to achieve specific impedance targets.

-

Differential pairs must be symmetrically routed with consistent spacing to maintain their impedance, with special care to avoid discontinuities caused by components or vias.

-

OrCAD X simplifies controlled impedance design by integrating analysis tools that automatically adjust trace parameters based on specified impedance values, helping ensure signal integrity and reliable performance.

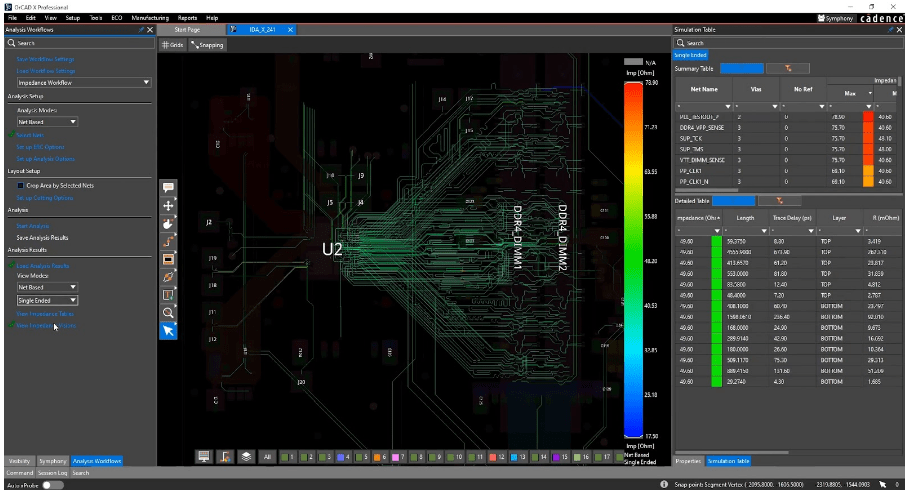

Use OrCAD X for impedance analysis of all nets in the design.

Controlled impedance refers to the management of the characteristic impedance of a PCB transmission line formed by traces and their associated reference planes, essential for maintaining signal integrity at high frequencies by preventing signal distortion. It is determined by the physical dimensions and dielectric materials of the PCB and is measured in ohms (Ω). Read on as we discuss tips in this controlled impedance design guide.

Common PCB transmission lines requiring controlled impedance include single-ended microstrip, single-ended stripline, microstrip differential pair, stripline differential pair, embedded microstrip, and coplanar lines (both single-ended and differential). Achieving controlled impedance involves matching substrate material properties with trace dimensions to ensure the impedance remains constant along the entire PCB path—from source to destination—regardless of trace routing or layer changes.

When You Need Controlled Impedance

Controlled impedance is essential for PCBs in high-speed digital applications, like RF communication, telecommunications, computing with signal frequencies above 100MHz, and high-speed signal processing in systems like DDR, HDMI, and Ethernet.

Single-Ended vs. Differential Trace Impedance

It’s important to differentiate between these two types. Single-ended signals, such as those in parallel RGB LCD or camera interfaces, require routing with a specified single-ended impedance, which measures the impedance between the trace and its reference ground. In contrast, differential pair signals, like SATA, PCIe, HDMI, and USB, must be routed with differential impedance.

Controlled Impedance Design Guide: Board Parameters to Tune

|

Category |

Details |

|

Stack-Up Design |

- The designer must develop the board's stack-up and calculate trace values for differential pairs and single-ended nets. |

|

Trace Width |

- Width of the copper foil on a PCB and its coating. |

|

Copper Thickness |

- An increase in copper thickness leads to a decrease in impedance. |

|

Dielectric Properties |

- Increase in dielectric thickness usually results in modest increases in impedance. |

|

Dielectric Constant |

- Ratio of the electric permittivity of a material to that of a vacuum. |

|

Other Trace Configuration Impedance Factors |

- Trace configuration (microstrip, stripline, differential pair). |

Planning and Specification Steps for Controlled Impedance

|

Design Aspect |

Key Points |

|

Specifying Layers and Target Impedance |

|

|

Controlled Dielectric Thickness |

|

|

Impedance Control |

|

|

Determining Which Signals Require Controlled Impedance |

|

|

Annotating the Schematic with Impedance Requirements |

|

|

Determining Trace Parameters for Controlled Impedance |

|

|

Distinguishing Controlled Impedance Traces from Other Traces |

|

Routing and Layout Practices for Controlled Impedances

|

Design Aspect |

Key Points |

|

Maintaining Symmetry in Differential Pair Routing |

|

|

Adequate Spacing Between Traces and Components (3W and 2W Rule) |

|

|

Placement of Components, Vias, and Coupling Capacitors |

|

|

Length Matching of Differential Pairs |

|

|

Reference Layers for Return Path of Controlled Impedance Signals |

|

|

Adding Stitching Capacitors and Vias |

|

|

Managing Return Paths Over Split Planes |

|

|

Minimizing Via Usage in Differential Pairs |

|

|

Avoiding Routing Over Plane and PCB Borders |

|

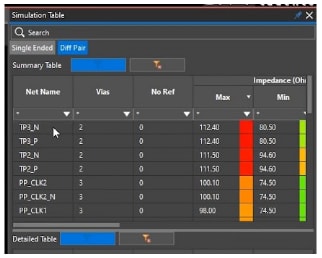

OrCAD X shows you impedance values (max and min) for individual traces.

Controlled Impedance Design With OrCAD X

Starting from release 24.1, OrCAD X integrates analysis tools directly into the design environment, streamlining controlled impedance design. You can perform both impedance and coupling analyses without external calculators or complex equations.

- For impedance control, you access the Setup > Cross-section editor, where you can define your PCB's layer stackup, including layer thicknesses, dielectric constants, and reference planes.

-

By specifying your target single-ended or differential impedance values, OrCAD X automatically recalculates the necessary trace widths and spacing. For instance, setting a target single-ended impedance of 50-Ω will prompt OrCAD X to adjust the trace width accordingly, accounting for variations between outer and inner layers due to differing dielectric materials.

Impedance Design for Differential Pairs in OrCAD X

For differential pairs, you can define the coupling type—typically edge coupling—and set your desired differential impedance, (e.g.90-Ω for USB 3.0 applications). OrCAD X then asks whether to recalculate the line spacing or trace width based on your preference to maintain certain manufacturing constraints, like minimum trace widths to avoid extra fabrication costs. The software presents impedance results through color-coded overlays on your design and detailed tables showing minimum, maximum, and typical values for each net or segment, allowing you to quickly identify and address any mismatches.

OrCAD X also allows you to extract and model any net or differential pair into the Topology Explorer for advanced simulation and to enforce ideal interconnect constraints. This holistic approach empowers you to model different interconnect scenarios, simulate their performance, and apply constraints directly within your design environment. With OrCAD X's integrated analysis capabilities, you gain confidence that your PCB will meet controlled impedance requirements and function reliably in high-speed applications.

These integrated analysis tools help you follow the steps outlined in our controlled impedance design guide. To learn more, explore our PCB Design and Analysis Software and discover how OrCAD X can enhance your design workflow.

Leading electronics providers rely on Cadence products to optimize power, space, and energy needs for a wide variety of market applications. To learn more about our innovative solutions Subscribe to our newsletter or subscribe to our YouTube channel.