PCB Design Strategies: Designing for High-Pin Count Devices

High Pin-Count Devices Using Plated Through-Hole Technology

As the devices shrink in pitch and increase in pin count, current density becomes a concern. The outer rows of the devices typically have lots of signal pins, while the pins in the center focus on power and ground. What that means out on the edges is that we have to use the first few layers of the board specifically for fan-out.

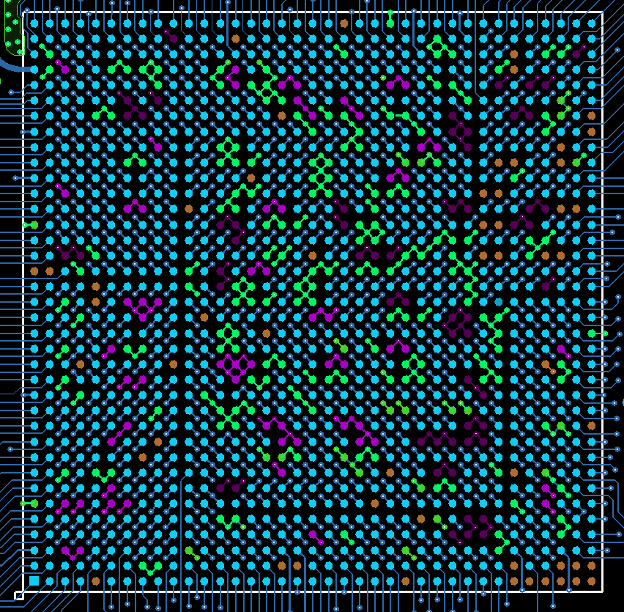

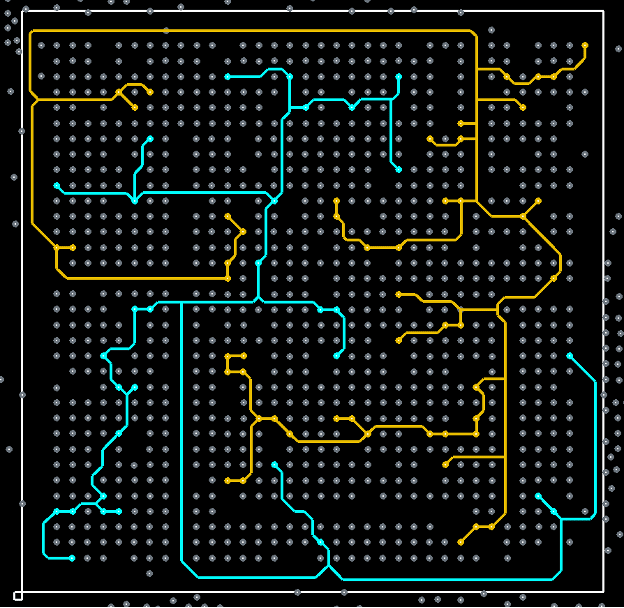

Figure 1. Just your average 1369 pin FPGA using a 1.27 mm (.05") pitch. In terms of colors, Green is our primary ground domain. Deep purple represents where we want heavy metal for high current. The lighter magenta is a lower wattage, more spacey kind of metal like Pink Floyd and the orange? Well orange you glad those are the no-connect pins? With that, let's dig into the fan-out.

One of the worst things you can do when faced with a BGA of 1000 pins is to drop a via deep into the board for pins on the edge of the device. I'd be ready to use every lane of the first three layers with layer 2 routed in the air gaps of the other two.

The point is to get away from the device until the trace gets a chance to join the normal flow of the routing channels. You have two distinct areas. One is the fan-out zone and then everything else where up, down, left and right make sense.

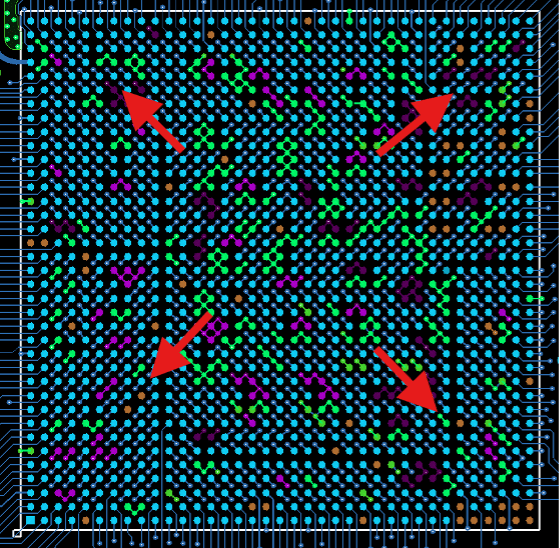

Figure 2. First thing is to address the outer ring(s) where we used the top layer to escape to a via for internal routing layer or to a nearby component that you placed there for that reason. The arrows indicate the fan-out flow; always away from the core. For the sake of rework, (and room for the fan-out) a component free area around the device will make it easier to desolder if it needs to be replaced. Otherwise, the tech has to remove the nearby components first. Image Credit: Author

Find your beach, drop a via that takes you to a level where the current is going your way. Until you have the vast majority of the connections handled in that way, it makes no sense to route between component clusters. Fan out is early in the timeline and updates to the schematic are probably on the table. It's much easier to move or edit a group while it is isolated from the rest of the board.

The outer ring of pins should be routed to "anywhere but here" using the outer layer of the board. If there is room to route between the pins, then the second ring of pins should escape on the outer layer as well. If there is no room for that, like with a 0.4 mm pitch, then the next layer down is best even if that is the traditional ground layer.

Conventional wisdom says that you would route orthogonal to the traces on the adjacent layers. In reality, that's a non-starter on the edges of a pin field. The direction of routing is to radiate away from the center of the device far enough that you can get to the component that was conveniently placed around the device or to a via where we can start to adhere to the regular routing in accordance with each layer's purposes.

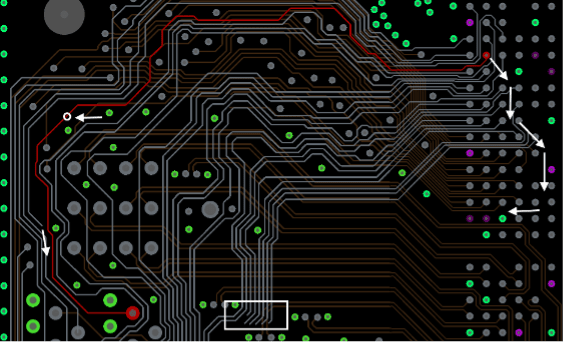

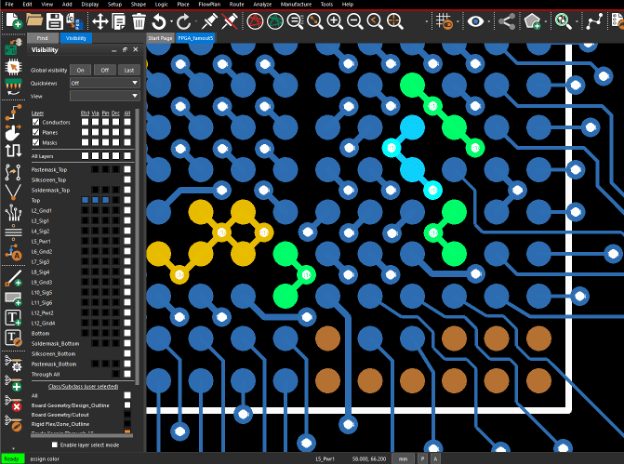

Figure 3. This trace in red is eating too many vertical routing channels. One option is to drop a via in the upper left corner and wrap around the differential pairs on the horizontal routing layer. The other option is use the same brown layer all the way and follow the arrows on the right side routing under the FPGA to the point where only two traces pass through the fan-out vias. From there, the routing goes all the way around the highspeed lanes. The first option seems like less work. Image Credit: Author

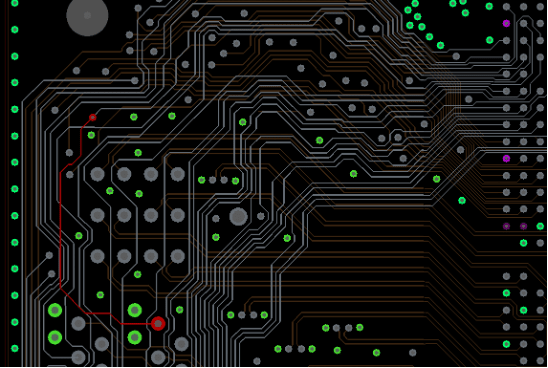

Figure 4. The strategy around horizontal and vertical routing layers is knowing when we can break away from the trend. The little box full of dangling lines has enough lanes to proceed with a minor revision to the trace. Obstacles such as shields, slots and board edges can be a place to route counter to the prevailing directions as a matter of necessity. Image Credit: Author

If there are external oscillator pins on a PMIC device, they are likely buried deep inside the BGA pin field rather than out on the perimeter where we like them. Are you going to have headroom for a crystal on the far side of the board? You might end up with some internal routing to get to the crystal.

If that's the case, I'd be using a guard band around those traces. Like almost every other component, there is a good reason to place the PMIC near the SOC. It's the same reason a single regulator is placed near the pins that make use of the power provided to any chip. It's a source of signal degradation that should be minimized. In the case of a PMIC, there are a number of such concerns.

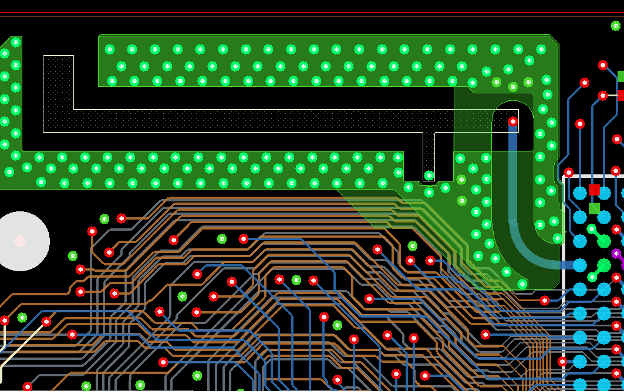

With the power domains and the essential routing behind us, we can finally close the schematic and play connect the dots using the two inner layers for up/down and side to side routing lanes. There are no length or width requirements left for the unrouted segments. My guess is that the average person would think that this is the nature of most if not all routing solutions. This has become less and less of a thing as the percentage of constrained nets has grown over time.

Figure 5. Both power domains can be connected without overlap. If it wasn't obvious before, it's now clear that we can supply the two main power domains with shapes on this layer based on the routing study. The shapes will fill in to distribute the voltages with minimal neck-down. (As we would most likely be using dynamic copper for the power planes, the traces would remain as a backbone.Though they are not even close to sufficient in terms of width they will prevent a future trace from splitting the plane entirely - in case additional routing ends up on this layer.) Image Credit: Author

Closing up those last traces can be a chore as all of the good routing channels seem to be taken. There are times when the routing goal is "anywhere but here". You might start at both ends and route a meander as far as it will go in any direction. Along the way you might have to be "impolite" with the existing work. If you can get the two ends to cross each other at some point, then the routing solution is only a via away. On a 95% routed board, that still may be a problem. I remember spending 20 minutes clearing out space to add one ground via. Such is life under an NFC chip of a phone.

The fan-out is a chance to make minor adjustments to the placement. This effort continues throughout the fan-out and routing steps. There's always some guesswork as we go about making design decisions. We're not always right but we're always ready to make it right when new information comes to light.

Figure 6. Re-examining this unused MIPI corner getting two more vias out of the grid. If you can only route one trace between pins/vias, then make sure you do just that. Get a trace through every gap. We can depressurize the inner layers in the same way. This applies to pin grid connectors as well as BGA devices. Maximizing each layer's number of connections is how we reduce layer count to something more feasible. Image Credit: Author

Let's Talk About Preliminary Routing

Cross probing and selectively displaying or colorizing nets gives us insight on what's to come. Even though we've checked off on the placement gate, it's a good idea to maintain elasticity for as long as possible. Modularity is useful when the inevitable update makes it necessary to relocate or rotate a device and its constituent parts.

That said, we have to begin connecting the various devices at some point. The heaviest hitting device on the board is a good place to start. It could be key because it uses the most power or has the most interconnects. It may also be the main amplifier or whatever motivates the product. Some device lies at the heart of every board so that's where the risk management begins. You have to start somewhere.

Step one will be the highest priority net on the highest priority chip. It will all be downhill from there; working towards the least significant connections. Operationally, I might not even place pull-up resistors until I've done the pin-escape from the device. Once the trace is fanned out and routed to a clear spot for the via, then the low priority part can land. The same can be said for test points. Get away from the dense area and find a home for the test pont.

Figure 7. There are times when everything else must step aside and clear all layers for a printed antenna. I would use a net short property to tie the antenna shape and the ground via so that the two can coexist at DC and the antenna's frequency. Like most of these slides, this one is made up entirely from scratch. The takeaway here is ground vias are always in demand around features like this one. Image Credit: Author

Like going back to the good old days, we're using the organic, free range kind of intelligence that comes straight from our brains. Sometimes it helps to flip the bit. Mirror the board's image. Soften the color pallet. Make it easy on yourself. I hope that many of you remain blessed with the option to work from home.

Either way, one of the things to consider when doing the fan-out is via stubs. If the chip is on layer one, then the higher layer numbers are the best bet for diff-pairs and such. If the route is on layer 3, then there will be a stub from 3 to the bottom. You don't want back drilling if you can avoid it. It can become a signal integrity thing as the layer count increases. With that advice, I'm going to move on to high density interconnect (HDI) implementation for the remaining studies.

Read Part Two Here: High-Density Interconnect (HDI) Techniques