Microvia Reliability in High-Density Designs

Key Takeaways

-

Microvias are prone to failure due to thermal stress and material mismatches.

-

Staggered microvias and larger diameters improve reliability during reflow and thermal cycling.

-

OrCAD X offers advanced tools for HDI routing, real-time checks, and thermal simulations to mitigate microvia failures.

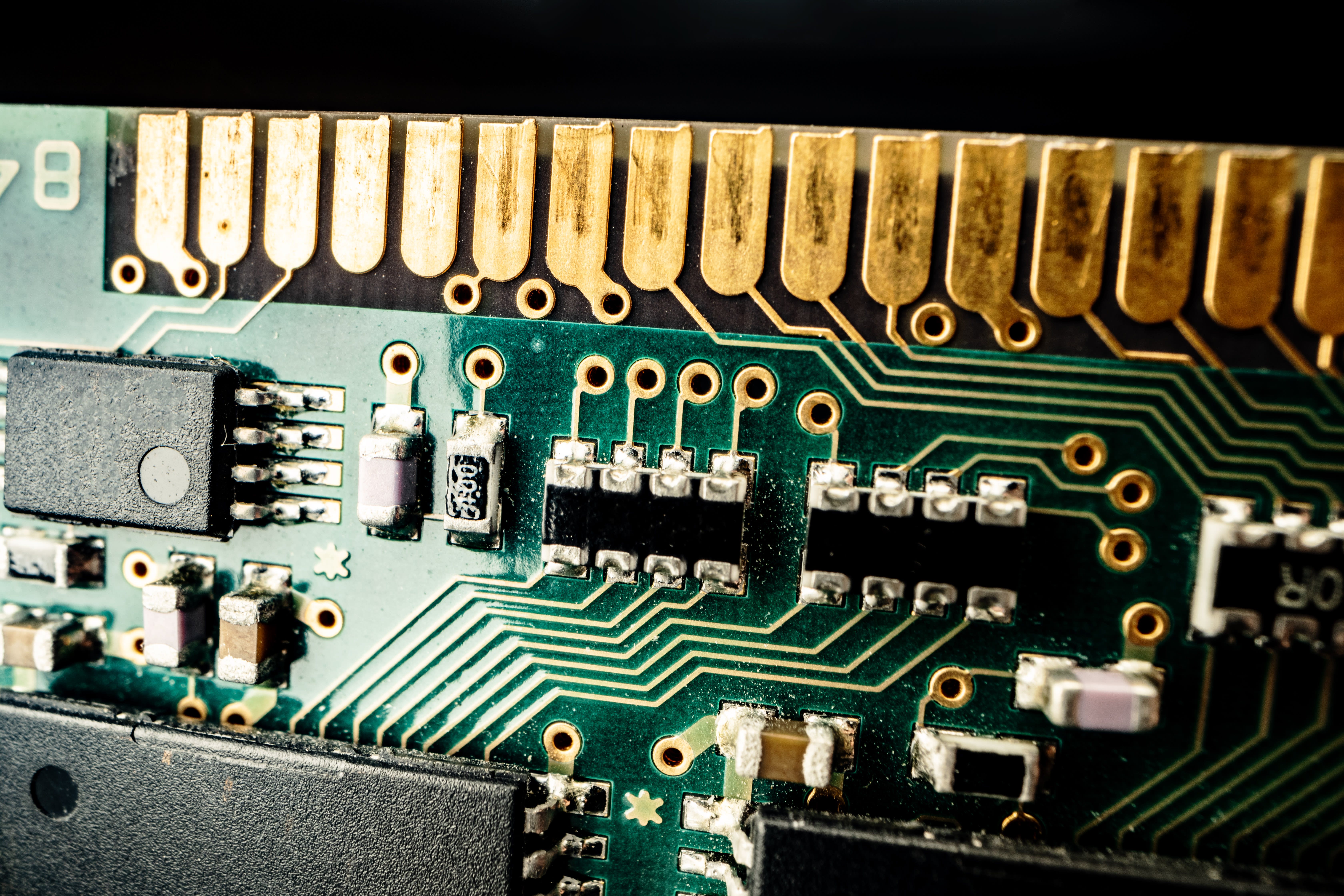

PCB with a variety of vias.

As high-density interconnect (HDI) designs with larger layer counts become more common, so has microvia use. In builds with configurations like 3+N+3 or greater, sequential laminations now often rely on skip vias, staggered microvias, and stacked microvias. However, one of the key challenges is that microvias are considerably more prone to failure compared to plated through holes. The smaller size of microvias and their incomplete depth make them more vulnerable to stress, which increases the likelihood of failure during reflow, accelerated testing, or real-world operating conditions. Read on as we discuss causes and solutions for microvia reliability issues.

|

Factor |

Details |

|

High-Temperature Dielectric Materials |

|

|

Expansion Rate Mismatch |

|

|

Multiple Lamination Cycles |

|

|

Reflow Stress |

|

|

Buried Vias |

|

|

Thermal Limits of Material |

|

|

Preconditioning and Resistance Changes |

|

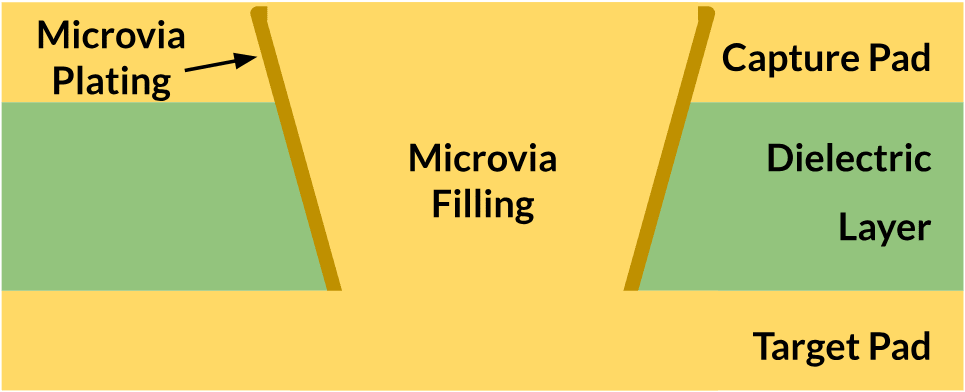

Basic microvia diagram.

Standards for Microvia Reliability

The IPC has developed stringent testing methods for microvia reliability, outlined in IPC-TM-650, see methods 2.6.27 and 2.6.7.2.

-

Method 2.6.27 involves subjecting a test vehicle or coupon to a standard solder paste reflow profile with peak temperatures of either 230°C or 260°C. Throughout six full reflow cycles, the coupon is connected to a 4-wire resistance measuring unit to monitor for any increase in resistance, which must remain under 5%. The daisy chain in the test coupon is composed of features used in actual circuits to simulate real-world conditions.

-

Method 2.6.7.2 introduces thermal shock testing, where the test coupon undergoes 100 thermal shocks between -55°C and 210°C. Resistance is monitored every second during reflow and once per cycle during thermal shock testing. If resistance increases by more than 5%, the device is considered to have failed.

Design Guidelines for Reliable Microvias

Choose Laser-Drill-Compatible Dielectric Materials

Laser drilling creates precise, V-shaped holes, which makes the plating process smoother and more effective. To prevent uneven heating and material inconsistencies, select dielectric materials that are compatible with laser drilling. Some recommended materials include:

-

Isola FR408HR: A high-performance, low-loss dielectric material known for its excellent thermal and mechanical properties, ideal for high-speed digital and RF applications.

-

Isola FR370HR: Designed for high-temperature reliability, this material is suitable for use in multilayer PCB designs that require thermal performance and durability.

-

I-speed: A high-speed, low-loss laminate with stable dielectric properties, offering improved signal integrity and lower transmission losses, particularly in high-frequency applications.

-

Nelco N7000-2HT: A high-temperature, low-loss dielectric material that excels in high-speed and high-frequency applications, providing superior electrical and thermal performance for complex PCB designs.

Follow IPC-T-50M Microvia Standards

The IPC-T-50M standards provide essential guidelines for microvia design to ensure reliability. Key parameters include:

-

A maximum diameter of 6 mils

-

A maximum distance of 10 mils between the capture pad and the target pad

Favor Staggered Over Stacked Microvias

Staggered microvias are more resilient to thermal cycles compared to stacked microvias. When designing staggered microvias, ensure the vertical separation between them is greater than the hole diameter. This spacing helps to reduce stress and improve reliability during thermal cycling.

Follow IPC-2226 Stack-up Standards

Selecting a PCB stack-up configuration that complies with IPC-2226 standards is vital for manufacturability and cost-efficient production. Below are various IPC-2226 stack-up types that support microvia reliability:

-

Type I: A PTH and a single microvia layer on one or both sides of the core.

-

Type II: A PTH, buried via, and a single microvia layer on one or both sides of the core.

-

Type III: Includes a PTH, buried via, and at least two microvia layers on one or both sides of the core.

-

Staggered Type III: Features staggered microvias with at least two microvia layers on one side of the core.

-

Capped and Staggered Type III: Has staggered microvias with capped outer layers and two PTHs, one of which is capped.

Ensure Zero Clearance Between Solder Mask and Microvias

To prevent solder bridging during the reflow process, it is essential to eliminate any gap between the solder mask and the microvia. Solder can flow into these gaps, causing unintended connections between adjacent traces, a critical design flaw that must be avoided.

Use Simulation Tools for Microvia Reliability

Simulation tools, like Gauss Stack’s Microvia Reliability simulation, offer designers the ability to predict and mitigate potential issues before building costly test boards. This rapid simulation environment allows you to model various scenarios, helping to optimize design choices and avoid time-consuming trial-and-error testing.

Optimize Microvia Dimensions and Pitch

The size and spacing of microvias are critical to the overall reliability of the PCB. Larger microvia diameters—especially those of 6 mils or more—are more resilient to thermal stress. Similarly, increasing the pitch (distance between microvias) to at least 10 mils minimizes the risk of failure due to copper cracking or substrate detachment during thermal expansion.

Balance Microvia Density and Reliability

While larger microvias and wider pitches improve reliability, they also reduce the available board space. Designers must carefully balance microvia size and pitch with the need for compact routing, especially in high-density applications such as aerospace and military electronics, where reliability is paramount.

-

Use microvia diameters of 6 mils or greater.

-

Maintain aspect ratios below 0.75:1, with a preference for 0.64:1 or lower for optimal reliability.

-

Ensure a minimum pitch of 10 mils between microvias.

Additionally, staggered microvia arrangements should be favored over stacked microvias, especially in designs undergoing significant thermal cycling. Staggered configurations have improved reliability and yield, even in challenging environments.

Consider Thermal Stress During Reflow

The reflow process is particularly harsh on microvias, subjecting them to extreme heat. Larger microvias with lower aspect ratios are better able to survive the thermal cycling that occurs during reflow. For designs that require lead-free soldering, which involves higher reflow temperatures, or those with multiple reflow cycles, larger microvias and wider pitches are recommended to mitigate thermal stress.

Methods Where Microvias Fail

Microvia failure modes encompass various flaws arising from material and process discrepancies. Here's a succinct overview of common microvia failure modes:

-

Microvia to Target Pad Separation: This separation often results from thermal stress and physical strain. It usually starts at the dielectric foot at the microvia base. This separation can lead to failure during cooling cycles, with the potential for cracks.

-

Barrel Cracks can occur within the cylindrical section of the microvia, typically during thermal cycling's heating phase. These cracks are linked to thin copper plating and can be exacerbated by plating issues, predisposing the microvia to cracking.

-

Corner Cracks: These cracks form at the interface between the capture pad and the target pad due to z-axis expansion. Although relatively uncommon, they represent a wear-out type failure that may arise from other design or material flaws.

-

Circumferential Cracks, developed around the base of the micro via within the capture pad due to mechanical and thermal stresses, challenge the micro via's integrity.

-

Microvia Misregistration: This involves the misalignment of the microvia with its intended position on the pads, leading to potential electrical failures such as open or short circuits.

-

Target Pad Pull Out: Occurs primarily in flex circuits with high CTE and low Tg materials like acrylic adhesive, leading to vertical and circumferential cracking around the target pad.

-

Copper Voids: These voids in the copper fill of microvias can compromise structural integrity, particularly when large enough to impact the wall thickness of the microvia barrel.

-

Copper Cap Separation: In stacked microvias, separation of the copper cap due to differing expansion rates with the dielectric can disrupt the conductive path and lead to failure.

How OrCAD X Can Lead to More Reliable Microvias

|

OrCAD X Feature |

Description |

Reasoning |

|

HDI Routing with Microvia Support |

OrCAD X provides advanced HDI (High-Density Interconnect) routing tools, allowing users to add blind, buried, and microvias with ease. The constraint manager automatically selects the correct via based on design rules. |

Proper selection and placement of microvias are critical for reducing stress on microvias during reflow and thermal cycling, improving reliability. |

|

Stacked and Staggered Microvias |

OrCAD X enables designers to define rules for stacked, staggered, or skip microvias in the constraint manager, ensuring that microvia arrangements meet reliability standards. |

Staggered microvias are preferred for better thermal cycle reliability, as they reduce stress between layers and improve overall durability. |

|

Real-Time Constraint Driven DRC Checks |

The OrCAD X constraint manager provides real-time feedback on spacing, via placement, and material usage, alerting designers to any potential violations. |

Instant feedback during design helps prevent violations that could lead to increased mechanical or thermal stress on microvias. |

|

Cross-Section Editor for Stack-Up Design |

OrCAD X allows detailed layer and material configuration using the cross-section editor, including dielectric properties and material thickness, crucial for controlling thermal expansion. |

Proper layer and material configuration ensure that thermal expansion rates between materials are well managed, preventing stress-induced failures. |

|

Thermal Simulation Tools |

Thermal analysis tools used in conjunction with OrCAD X help simulate heat distribution across the board, identifying areas of potential thermal stress on microvias. |

Manufacturing defects can significantly reduce the lifespan of microvias, and DFM checks help ensure designs are ready for reliable production. |

|

Constraint Management for HDI Designs |

OrCAD X supports detailed constraint management for HDI designs, including defining specific rules for microvia diameter, pitch, and aspect ratios. |

Ensuring correct microvia dimensions and placement is critical to preventing failures related to high current density and thermal cycling. |

|

DFM (Design for Manufacturability) Checks |

OrCAD X includes DFM checks, ensuring that microvias meet manufacturing tolerances and reliability standards, helping avoid defects during production. |

Manufacturing defects can significantly reduce the lifespan of microvias, and DFM checks help ensure designs are ready for reliable production. |

To ensure microvia reliability in PCB designs, engineers should focus on challenges such as thermal stress, material expansion, and copper integrity. Cadence OrCAD X provides advanced features like HDI routing, real-time DRC checks, and thermal simulation, allowing designers to optimize microvia arrangements for improved durability. Learn more about Cadence PCB Design and Analysis Software and explore OrCAD X for your next project.

Leading electronics providers rely on Cadence products to optimize power, space, and energy needs for a wide variety of market applications. To learn more about our innovative solutions, talk to our team of experts or subscribe to our YouTube channel.