Constraint Management for Impedance Control in High Speed Design

Key Takeaways

- Impedance mismatches result in reflection and desynchronization of signals in parallel nets, leading to bit errors at a receiver.

- Quickly identifying impedance violations requires a constraint manager in your PCB design tools. You can then set impedance limits and tolerances in as design constraints.

- Post-layout simulation tools can be used to inspect nets that don’t conform to impedance constraints and identify areas where the design should change.

Use constraint management for impedance control and spotting reflections

Trace impedance control is a simple matter of properly sizing traces. When a single trace is considered in isolation, its impedance will have a well-defined value. However, when brought near another trace or conductor, the impedance of the trace will be different from its designed value due to unintended coupling. This annoying fact produces impedance variations along an interconnect, and extreme impedance mismatches between a transmission line and receiver will lead to signal reflections.

Although you’ve likely routed your PCB layout with best practices and only used the designed trace width for routing, you can still be at risk of impedance variations in an interconnect. This is where constraint-drive design provides the benefit of checking your board against your design constraints as you route your layout. If you’re bringing up an older board and you need to check impedance in batches, you can run a batch DRC and browse through impedance violations.

When you’re ready to correct any impedance errors throughout your board, the post-layout simulation features in Sigrity give you the ability to analyze impedance throughout single-ended and differential interconnects. You can also spot reflections at specific locations along interconnects, such as at via or connector transitions. Here’s how this works in Allegro’s PCB layout tools and the Sigrity analysis features.

Defining Constraints for Impedance Control

Impedance control is all about ensuring the geometry of traces in your PCB is consistent throughout each interconnect. This applies to both single-ended and differential pairs. These constraints need to be defined to comply with your high speed signalling standards. These signalling standards, in turn, depend on the components you select or the type of interface you’re designing.

PCB design software is designed to be adaptable to ensure you can define any physical and electrical constraints in order to comply with DFM requirements and signalling standards. The design tools in Allegro allow you to define required impedance values and tolerances using the Allegro Constraint Manager. This tool can be accessed within Allegro PCB Designer or Allegro Sigrity SI.

In the forthcoming example, we’ll look at how to define and examine impedance constraints for a group of nets in an existing layout. The four nets we want to examine are shown below. These four nets are part of a DDR3 data bus and need to have 34 Ohm defined impedance. Here, we’ll check that these traces have impedance within limits under the JEDEC standard and that excessive reflections do not occur along these traces.

Four impedance controlled nets for analysis.

Defining Constraints

To get started defining constraints, we need to decide if constraints will be defined on individual nets, or on groups of nets. Allegro PCB Designer allows users to assign nets to a group, and the same set of design rules can be assigned to the entire group. Note that you’re not required to assign a net to a group; a net can have its own design rules and constraints. All design constraints can be accessed, viewed, and edited within the Allegro Constraint Manager.

To access the Allegro Constraint Manager and define constraints in your board, open your .BRD file in Allegro Sigrity SI. Click the Setup menu and navigate to Constraints → Constraint Manager. When you open the Constraint Manager, you can access group-based and net-based electrical constraints from the panel on the left side of the screen.

To set impedance constraints for a net group, open the Electrical Constraint Set option and navigate to Routing → Impedance. The image below shows the two net groups defined in this board. As both net groups are part of a DDR3 interface, the impedance of the traces on this interface should be set to 34 Ohms. The impedance tolerance has been set to 5%.

Impedance constraints for a net group.

The four traces we want to examine are not part of these net groups, but we could assign these traces to these net groups if we wanted. The other option is to define the impedance constraints on these traces individually within the Electrical Constraint Set. To apply the rule, simply scroll down to the Net section within the electrical worksheet in the Constraint Manager. When you open the Routing → Impedance section, you’ll be able to see all nets and which groups they belong to.

If you want to assign a net to an electrical clearance set, simply open the drop down menu in the Referenced Electrical C Set column and select the desired electrical clearance set. For now, we’ll assign target impedance values to the individual nets we want to examine. The image below shows the target impedance set to 34 Ohms with 5% impedance. Once the target impedance value is defined, we see that the net is flagged in red. If the net does not flag immediately, simply run a design rule check from the toolbar (select Update DRC under the Tools menu).

Impedance constraints for individual nets.

In the above image, these four nets are flagged red because the minimum and/or impedance values throughout these nets fall outside the 34 ± 5% range (32.3 to 35.7 Ohms). The Constraint Manager shows that the impedance ranges from 32.069 Ohms to 46.62 Ohms; these values could appear anywhere on these nets. This could occur due to unintended parasitic coupling with other conductors, variations in trace width, or routing over a gap in a reference plane.

Note that Allegro Constraint Manager also allows you to define several other physical and electrical constraints for your PCB. The physical constraints govern aspects like pad and trace spacing, while electrical constraints govern aspects like propagation delay limits and return path tracking.

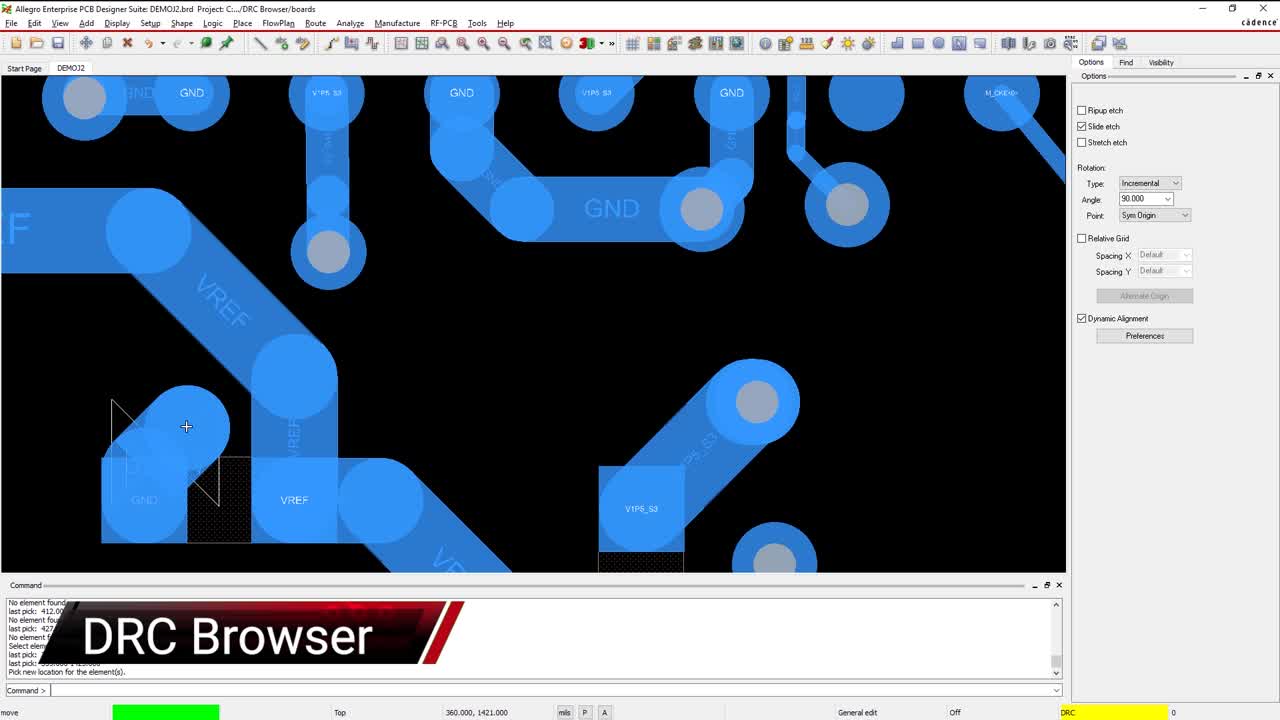

Once you’ve identified nets that violate design rules, you can get more detail on exactly which portions of the design violate your design constraints. Another way to view constraint violations is to use the DRC Browser from the Tools menu. This will show you coordinates in the board that violate a design constraint and will flag specific constraint violations in different categories. Reading through this list of violations can be cumbersome, but Allegro provides tools to visualize constraint violations. This involves some post-layout simulations from your layout data.

Running Impedance and Reflection Simulations

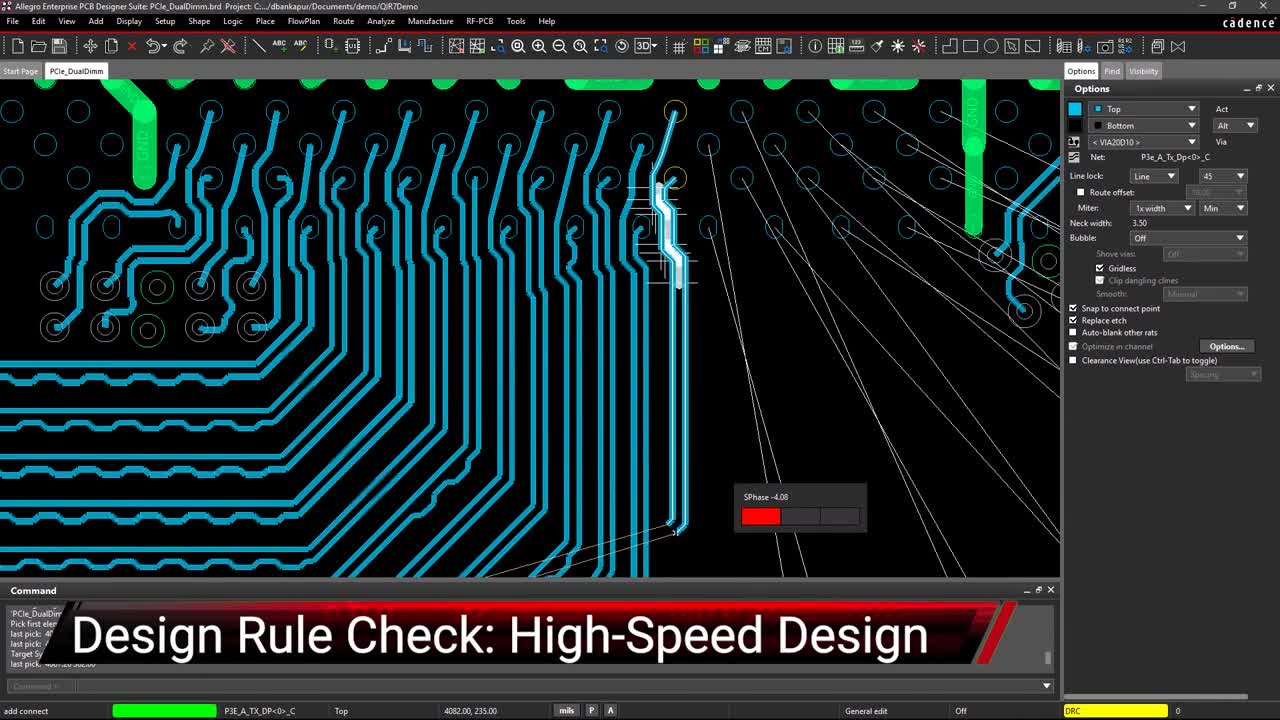

Once you’re ready to correct spot impedance mismatches in your board, you can use the signal integrity analysis features in Allegro to spot impedance variations and identify locations with reflections. To do this, open your board in Allegro , click the Analyze menu, and select the Workflow Manager option. This will bring up several analyses you can perform, including the Impedance Workflow and Reflection Workflow.

To get started, select the Reflection Workflow and the nets you want to examine. After selecting the nets, click Start Analysis to begin the simulation. Once the simulator finishes, you can click Reflection Vision to see a heat map that flags the location of reflections in your selected nets. You can also click the Reflection Table to see specific overshoot/undershoot values and their coordinates in the board. Since we are dealing with DDR lines on this board, the values can be compared against JEDEC specifications in the Reflection Table.

The image below shows some reflection results for the group of four nets we’ve been examining. From this image, we see that the reflections primarily occur at component pads. These values are flagged in red and only produce ~10 mV of ringback. The 30 mV ringback is seen earlier on the interconnects and are not easily visualized with the Reflection Vision tool; you need to double-click on the corresponding entry in the impedance table to see these results.

Reflection Workflow results.

The 30 mV ringback along these nets occurs at multiple points near the length matching segment shown in an earlier image. The Impedance Workflow analysis can help you explain these reflections as arising from impedance variations along the interconnect, which will become more obvious when seen visually.

To examine impedance variations, select the Impedance Workflow option in the analysis toolbar. Select the same nets to analyze and run the simulation. The impedance throughout the interconnect can be viewed by selecting the Impedance Vision option, which will again show a heat map with color-coded impedance values.

Impedance variations on four nets.

From here, we can immediately see where the impedance makes an abrupt transition from ~46 Ohms to ~34 Ohms, just as was indicated in the Allegro Constraint Manager. This should be obvious from the length change between the red sections and the blue sections. This corresponds to the region with higher overshoot in these nets. Here, your next step is to compare your signal overshoot and impedance variations against your signalling standards. The red portions of these nets are part of a fanout from the BGA on an FPGA, so you’ll be limited in how wide you can make the fanout portion to prevent excessive reflections and losses.

The same simulation steps shown above can be used to examine different pair nets in your board. You simply need to select both ends of the pair to ensure the differential impedance remains consistent throughout the board. With differential pairs, you also need to examine conformance to length matching tolerances, which can be defined in the Allegro Constraint Manager. The DRC Browser can then be used to determine where length matching violations have occurred, and the routing tools will let you apply standard length matching segments to keep your differential pairs synchronized.

If you’re looking to learn more about how Cadence has the solution for you, talk to us and our team of experts.