Transistor Biasing and Output Bias Voltages

Key Takeaways

-

Transistor biasing makes analog and digital operation of a transistor possible.

-

Without transistor biasing, BJT amplifiers fail to deliver the required output across load terminals.

-

The optimum value of transistor bias voltage is equal to two times the required AC output voltage peak. If you vary the transistor bias voltage, the Q-point will also shift its position.

A phone with a dead battery is like a transistor that has not been properly biased

Yesterday, I happened to dial my aunt after a really long gap. She kicked off a long one-sided conversation mixed with complaints and bits of advice on my busy schedule, health, kids, etc. After a few minutes, I was ready to end the conversation, but there was no sign of anything stopping her from the endless lectures. Fortunately, her battery died and I was saved.

This situation can be well mapped to a transistor without proper transistor biasing. Transistor biasing (DC biasing) is the process of providing appropriate DC voltage or current to a transistor for its proper functioning in an electronic circuit. The transistor acts exactly like a dead phone when there is no DC bias. Whatever be the application, a stabilized DC bias is a must for proper transistor functioning. Let’s see how biasing defines the transistor operation.

Transistor Biasing and Operating Region

The Bipolar Junction Transistor (BJT) operates as either an analog device in applications such as amplifiers, oscillators, etc. or a digital device in converters and switching circuits. This dual action of the transistor is realized by transistor biasing.

The biasing applied to the two PN junctions of the transistor influences the movement of majority carriers and thus the behavior of the transistor. The biasing for a transistor to operate in an amplifier is entirely different from that in a transistor-based converter. Table.1 gives details about the region of operation and bias conditions at emitter and collector junctions when a transistor operates as an analog and digital device.

Table.1 The region of operation and bias conditions in a transistor

*( FB-Forward Bias, RB- Reverse Bias)

The biasing circuits for transistor switches are generally called base drive circuits. We are discussing transistor biasing in the context of a transistor amplifier.

The Secret Behind the Transistor Amplifier

Normally, the transistor amplifier shares a common terminal between its input and output and the three possible configurations are given in Table.2.

Table.2 Transistor configuration details

Figure.1 Basic CE amplifier

Let’s catch a CE silicon NPN transistor amplifier (shown in Figure.1) in action. The E and C junctions can be supplied from a single dc voltage Vcc as it fulfills the major purpose of supplying the input transistor current. When an ac signal Vin is superimposed with the bias voltage VCC, it similarly varies IB with respect to time. The relationship given in Table.2 for the CE amplifier is obeyed and Ic follows the shape of IB. The current gain denoted by in the transistor datasheet is the proportionality constant in the Ic - IB relationship. The voltage drop ICRL gives the ac output voltage Vout.

Do you think amplification is possible without DC bias? If so, disconnect Vcc from the base and predict Vout. We know that EB junction remains FB for only the instantaneous values of Vin > 0.7 V (EB voltage drop) and otherwise RB. Now combine this concept with negative half cycle and instants where Vin < 0.7. With all accounted for, you should be sitting at no voltage.

Determining the Optimum Bias Voltage

In Figure.1, the coupling capacitors Ci and Cc are included to block the DC components from the input and output respectively. If Cc is removed, the output voltage Vout gets a DC shift of Vcc voltage.

Now, if you want to design an amplifier to give an output ac voltage of 10 V peak, what bias voltage would you prefer? Is your answer equal to 10 V? Oh, no problem, we’ll figure it out step by step.

You know the voltages before and after Cc. It’s (10 V peak AC voltage + Vcc) and 10 V peak AC voltage respectively. If you are looking for symmetrical 10 V peak ac output voltage after Cc, the Vcc should be at least 20 V, right? If not, what happens? The output voltage Vout will be unsymmetrical and the peak value won’t meet the requirement. Confidently, we can say that the optimum Vcc should be 2 *( peak amplitude of desired Vout ). If you can add the transistor voltage drops and source resistances to the above calculation, then the Vcc becomes the most optimum.

Is Q-Point Susceptible to Transistor Bias Voltage?

Once Vcc is connected, IB starts circulating in the circuit (Figure.1). From Figure.2, it’s visible that for each IB, there exists a set of (VCE, IC) co-ordinates. The (VCE, IC) for IB supplied from Vcc at zero Vin is called the DC operating point or Quiescent point (Q-point). For a linear transistor amplifier, it is judicious to keep the Q-point in the middle of the active region.

Figure.2 Q-point is the intersection of the DC-load line and output characteristics of CE transistor

How to place the Q-point in the middle of the active region? This can be implemented by adjusting IB supplied by Vcc using a limiting resistor RB inserted between Vcc and transistor base. The bias circuit is designed with two considerations:-

-

IB should remain somewhere in the middle of the active region even when AC swings due to Vin are introduced. This guarantees the steady and linear operation of the amplifier.

-

The (VCE, IC) corresponding to these IB swings should be within (VCE, sat, IC, sat) limits given in the transistor datasheet.

There are many combinations of (VCE, IC) satisfying the above criteria in a chosen IB curve. Where exactly to fix the Q-point in this chosen IB curve? This can be solved by drawing the DC-load line. The line connecting the maximum possible Ic and VCE in the amplifier circuit is called the DC-load line.

Applying KVL to the output side of the amplifier (Figure.1) at dc bias conditions (Cc internal resistance ignored), we get

VCE= Vcc-ICRL (1)

The maximum possible IC and VCE are given by equations (2) and (3) respectively

VCE, max= Vcc at IC =0 (2)

IC, max= Vcc/RL at VCE =0 (3)

The intersection of the dc-load line with the chosen IB curve is the ideal Q-point for the faithful operation of your amplifier.

For a given amplifier, the Q-point shifts upwards with the rise in Vcc and vice-versa. Now, what is your inference about the Q-point of a transistor amplifier where Vcc is fluctuating continuously? Yes, exactly! We need a stabilized transistor biasing for distortionless amplification.

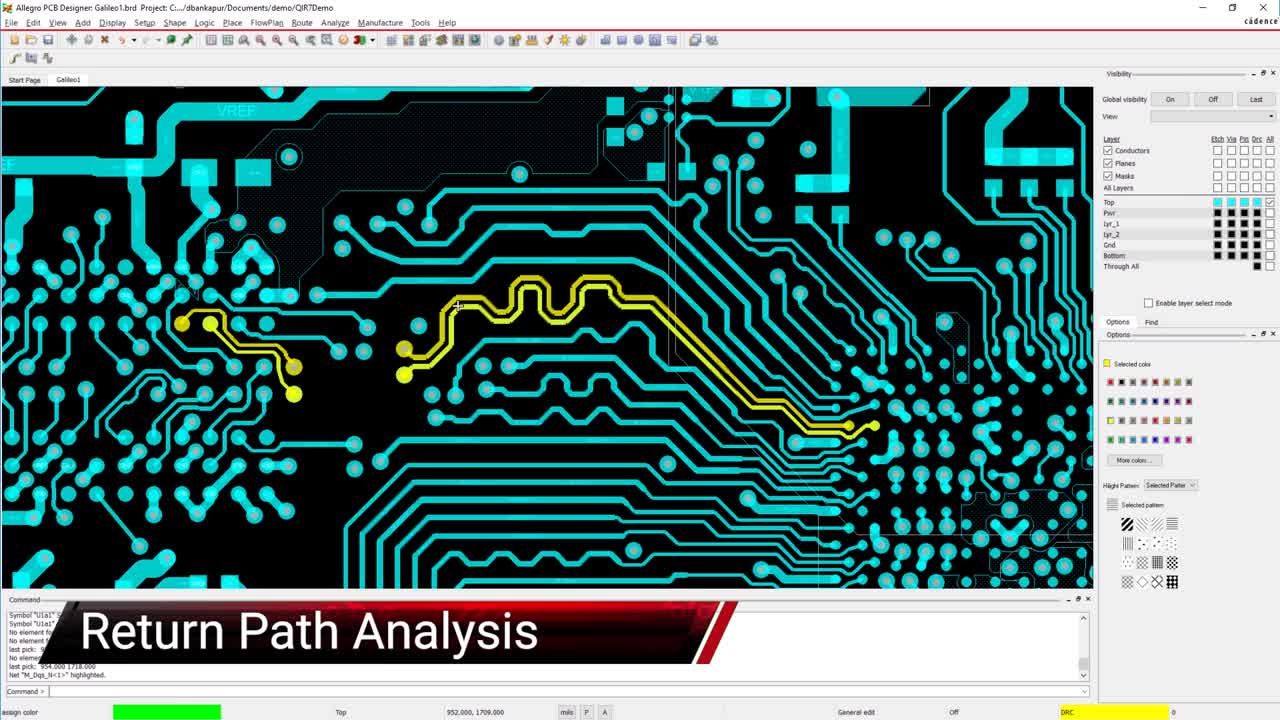

Bias Point Analysis

Sometimes finding smart shortcuts are fine. You can determine the Q-point as well as the voltages, currents, and power dissipated in different components of your amplifier by running the bias point analysis in a circuit simulation platform.

If you are running the bias point analysis on your circuit, you can easily fix the Q-point. The PSpice Simulator by Cadence can guide you to fix an ideal Q-point through its bias point analysis. You can access numerous circuit analysis features in this software that can help you fine-tune your circuit design and operation.

If you’re interested to get information about bias point analysis and other sophisticated toolsets in PSpice, talk to us and our team of experts.