Hardware Description Languages: VHDL vs Verilog, and Their Functional Uses

Key Takeaways

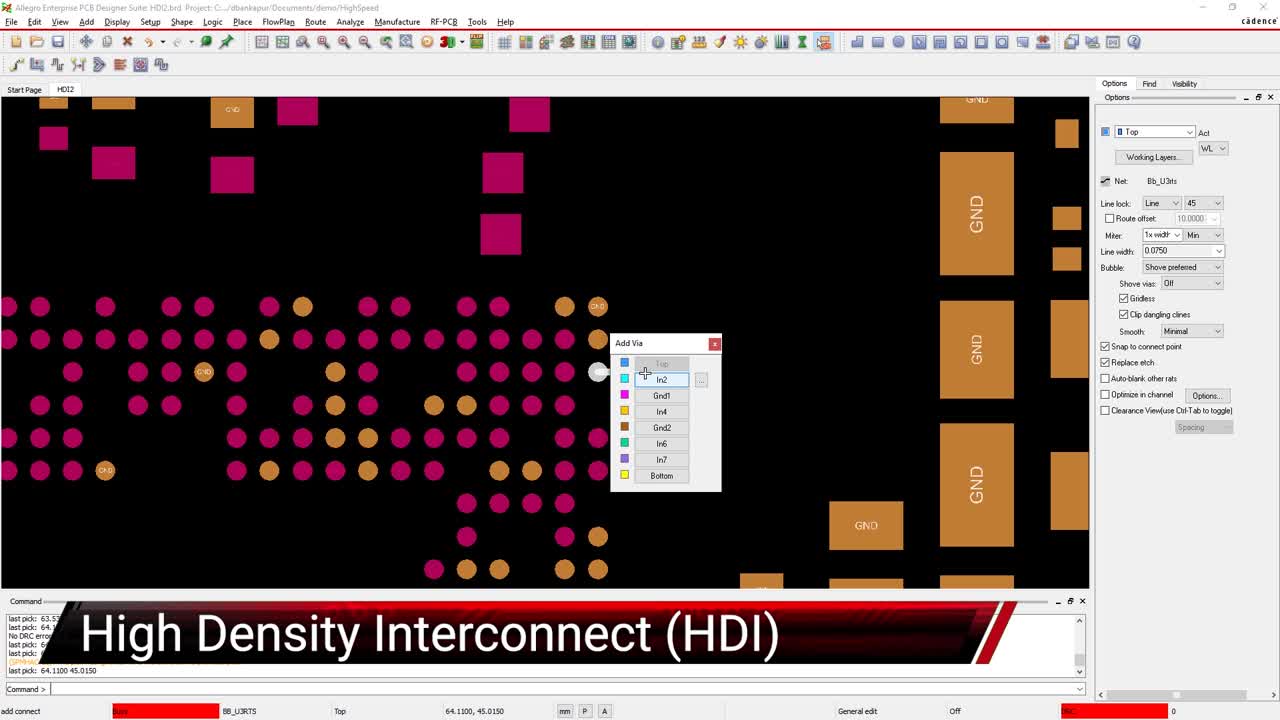

● Cadence's offerings for FPGA solutions.

● Learn about hardware description languages.

● Gain a greater understanding of the importance of HDLs.

● Learn more about the different types of hardware description languages.

VHDL affords quicker more accurate designs.

Language, by most metrics, is the foundation of any civilization or society. The field of electronics, which in a way is its own society, also utilize languages that are specific to its members. Two of these field-specific (hardware description) languages are VHDL and Verilog. Both are considered general-purpose digital design languages, each with subtle differences and advantages over the other.

What Are Hardware Description Languages (HDLs)?

HDLs are indeed similar to programming languages but not exactly the same. We utilize a programming language to build or create software, whereas we use a hardware description language to describe or express the behavioral characteristics of digital logic circuits.

We utilize HDLs for designing processors, motherboards, CPUs (i.e., computer chips), as well as various other digital circuitry.

What Is VHDL?

Very High-Speed Integrated Circuit Hardware Description Language (VHDL) is a description language used to describe hardware. It is utilized in electronic design automation to express mixed-signal and digital systems, such as ICs (integrated circuits) and FPGA (field-programmable gate arrays). We can also use VHDL as a general-purpose parallel programming language.

We utilize VHDL to write text models that describe or express logic circuits. If the text model is part of the logic design, the model is processed by a synthesis program. The next step in the process incorporates a simulation program to test the logic design. During this step, we utilize the simulation models to characterize the logic circuits that interface to the design. We refer to this collection of simulation models as a testbench.

Typically, a VHDL simulator is an event-driven simulator which means that we add each transaction to an event queue for a particular scheduled time. For example, if a signal assignment occurs after one nanosecond, we add the event to the queue as time + 1ns. Although a zero delay is allowed, it still must be scheduled, and for these scenarios we utilize a Delta delay.

Note: a Delta delay represents an infinitely small time step.

VHDL Functionality

These simulations alternate between two modes:

-

Statement Execution: In this mode, the triggered statements are evaluated.

-

Event Processing: During this mode, the events in the queue are processed.

Though there is an inherent similarity in hardware designs, VHDL has processes that can make the necessary accommodations. However, these processes differ in syntax from the parallel processes in tasks (Ada).

Similarly to Ada, VHDL is a predefined part of the programming language, plus, it is not case sensitive. However, VHDL provides various features that are unavailable in Ada, e.g., an extensive set of Boolean operators which include nor and nand. These additional features enable VHDL to precisely represent operations that are customary in hardware.

Another feature of VHDL is it has file output and input capabilities that you can utilize as a general-purpose language for text processing. Although, we typically see them in use by a simulation testbench for data verification or stimulus. Specific VHDL compilers build executable binaries, which afford the option to use VHDL to write a testbench for functionality verification designs utilizing files on the host computer to compare expected results, user interaction, and define stimuli.

Note: Ada is a statically typed, structured, object-oriented, and imperative high-level programming language; it is an extension that derives from Pascal and other programming languages. Its name, Ada, refers to Ada Lovelace (Ada King; 1815–1852), the Countess of Lovelace, who we credit as being the first computer programmer.

The Advantages of VHDL

The critical advantage of VHDL, with regard to system design utilization, is that it permits the behavior of the essential system to be verified and modeled in advance of the synthesis tools translation of the design into actual gates and wires (hardware). VHDL projects are also portable, which means that you can generate a project for one element base and then port it on another element base, such as VLSI, with a variety of technologies.

Using VHDL affords the user concurrent system descriptions. VHDL is a dataflow language, which means it can simultaneously consider every statement for execution. This is in direct contrast to procedural computing languages like C, assembly code, and BASIC. Each of these languages runs a sequence of statements, both sequentially and a single instruction at a time.

One of the more advantageous benefits of VHDL is that its projects are multipurpose; you create the project once and you can utilize the calculation block in various other projects. This means you have the ability to make changes, such as to parameters, element base, memory size, block composition, interconnection structure, and capacity.

What Is Verilog?

As I am sure you are aware, Verilog is also a Hardware Description Language. It employs a textual format to describe electronic systems and circuits. In the area of electronic design, we apply Verilog for verification via simulation for testability analysis, fault grading, logic synthesis, and timing analysis.

Verilog is also more compact since the language is more of an actual hardware modeling language. As a result, you typically write fewer lines of code, and it elicits a comparison to the C language. However, Verilog has a superior grasp on hardware modeling as well as a lower level of programming constructs. Verilog is not as wordy as VHDL, which accounts for its compact nature. Although VHDL and Verilog are similar, their differences tend to outweigh their similarities.

Verilog HDL is an IEEE standard (IEEE 1364). It received its first publication in 1995, with a subsequent revision in 2001. SystemVerilog, which is the 2005 revision of Verilog, is the latest publication of the standard. We call the IEEE Verilog standard document the LRM (Language Reference Manual). Currently, the IEEE 1364 standard defines the PLI (Programming Language Interface).

Note: The PLI is a collective of software routines that allows a bidirectional interface between other languages such as C and Verilog.

VHDL vs Verilog

Like the majority of choices one must make in the field of electronics, it typically centers around the functional advantages. In the case of VHDL vs Verilog, it is no different. One of these operational advantages VHDL has in comparison to the original Verilog is VHDL's full type system. This system affords designers the ability to write much more structured code, and this is particularly useful if declaring record types. In summary, there are varying opinions as to which language is superior, however, it really just comes down to personal preference.

Verilog affords faster, more accurate designs and verification.

Thankfully, with our PCB Design and Analysis overview page, you will be sure to have your designers and production teams working together towards utilizing the appropriate HDL for all of your company's design and manufacturing needs. If your company needs more information on the use of VHDL or Verilog or how they can benefit your company's designs, then view our What's New in Allegro PCB Design page.

Whether you are utilizing a single-sided board or a multi-layer design, you will need the right set of PCB layout and design software. Allegro PCB Designer and Cadence's full suite of design tools can help you create designs from verified component models and analyze all aspects of their functionality. You'll also have access to a set of tools for MCAD design and preparing for manufacturing.

If you're looking to learn more about how Cadence has the solution for you, talk to us and our team of experts. To watch videos about related topics or see what's new with our suite of design and analysis tools, subscribe to our YouTube channel.