What is a PCB Netlist

Key Takeaways

-

A netlist is a text file that defines a circuit's electrical connections for PCB design, simulation, and routing.

-

Types of netlists include physical, logical, instance-based, flat, and hierarchical, each serving specific design needs.

-

Common formats like SPICE, EDIF, and IPC-2581 ensure compatibility across EDA tools, while proper modification and documentation of netlists minimize errors and enable smoother integration during PCB design.

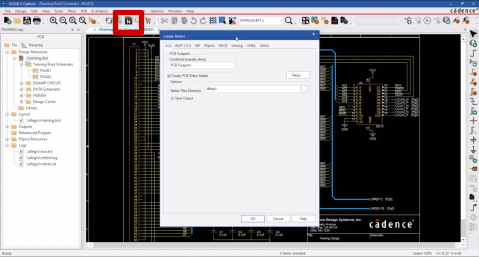

So you’ve created a PCB schematic using OrCAD X Capture, and you’re ready to move on to the next step in designing your PCB. How would you do that?

Well, if you’re like most PCB designers, chances are high you looked up a quick 2-minute tutorial video, or checked out our guide to generate a Netlist in OrCAD X and followed these steps in your PCB layout tool to start designing. But if you’re curious as to exactly what is a PCB netlist, and what’s going on behind the scenes when you create that intermediary file, this post is for you.

What is a PCB Netlist File?

A PCB netlist is an ASCII text file that defines a circuit’s electrical connectivity by listing all connections (nets) between component pins. Unlike a schematic, which visually represents the circuit with symbols and connections, a netlist focuses solely on conveying essential connectivity data for PCB layout, simulation, and other EDA tools. By eliminating visual elements, netlists enable automation, ensuring accurate and efficient communication between design stages while reducing errors in the transition from schematic to physical implementation.

Netlists can vary widely in terms of formats and the amount of information they convey. Here’s an example of the type of information that will be included in a netlist:

-

Reference designator (e.g., C1 for the first instance of a capacitor)

-

Pin numbers

-

Signal keywords (e.g. GND)

What follows is a simple example of a standard netlist produced by OrCAD X Capture:

|

*SIGNAL* NET1 |

|

U2.7 C2.2 U3.3 C1.2 U1.5 |

Netlists are pretty straightforward to read even if you’ve never encountered a particular format before. In NET1 above we can see that C2.2 refers to pin 2 of the second instance of a capacitor which is electrically connected to pin 7 of a part given the generic designator U2.

There will be a parts list preceding the netlist telling you what each designator is referring to, in this case, U2 refers to a dual in-line package.

Types of Netlist File

|

Type |

Description |

Use Cases |

|

Physical Netlist |

Based on actual physical connections; each wire is treated as a distinct connection. |

Used in PCB layout to represent real-world wiring and connectivity. |

|

Logical Netlist |

Focused on logical connections; multiple components connected to one terminal are treated as a single logical connection. |

Ideal for simulation and verification where logical behavior is more important than physical structure. |

|

Instance-Based Netlist |

Organized around component instances, clustering connections by each component. |

Common in hierarchical designs or when focusing on specific component behavior. |

|

Net-Based Netlist |

Provides an exhaustive list of all connections to a particular net, regardless of the components involved. |

Used in PCB routing or debugging specific nets in the design. |

|

Flat Netlist |

Displays all connections in an ungrouped, straightforward format. |

Simpler designs where readability and direct access to all connections are required. |

|

Hierarchical Netlist |

Groups connections logically, often by physical board, layer, or subcircuit. It can be folded (hide details in layers) or unfolded (show all details, similar to flat) |

Essential in complex multi-board systems or multi-layer PCBs. |

Common Netlist Formats

Common netlist formats include EDIF, IPC-2581, and SPICE.

EDIF (Electronic Design Interchange Format)[.EDIF]:

A vendor-neutral format designed to facilitate data exchange in EDA. It supports both netlists and schematics, enabling interoperability between various tools. EDIF was an early attempt to standardize EDA data formats.

SPICE [.CIR]:

It is commonly used for analog and mixed-signal circuit simulation. It describes the circuit components, nodes, and their interconnections in a textual format

PCB Netlist File Types in OrCAD X

Now you might be wondering, what type of PCB netlist files are used in OrCAD X? Well, OrCAD X is capable of handling various PCB netlist file types, ensuring seamless integration between schematic design, PCB layout, and manufacturing processes. As you design and go through your PCB workflow, OrCAD X will handle your PCB netlists automatically. But, in case you’re interested, we’ve outlined it below.

.LIB (Library File):

It maps logical components in a schematic to their physical PCB representations. It defines pin assignments and connectivity, ensuring consistency between schematic and layout.

-

Logical-to-physical mapping of schematic components to PCB footprints.

-

Contains reusable connectivity data, standardizing components across designs.

-

Often used alongside .DSN files to generate .NET files.

.NET (Netlist File):

This file lists all electrical connections (nets) between component pins, serving as a direct input to PCB layout tools. This ensures that the physical design reflects schematic connectivity.

-

Specifies component pin connections for routing.

-

Acts as the starting point for PCB layout tools.

-

Facilitates collaboration between tools (e.g., transferring design intent from OrCAD Capture to Allegro).

.MNL (Manufacturing Netlist File):

This is a manufacturing-specific netlist generated after the PCB layout process. It includes both design connections and physical attributes optimized for fabrication and quality assurance.

-

Contains pin-to-pin distances, impedance, and physical constraints.

-

Reflects the finalized PCB layout, differing from the schematic-based .NET file.

-

Used in automated testing systems for continuity and functionality checks.

Document Netlist Changes

Understanding how to read a netlist will help you troubleshoot errors that occur from using netlists from third-party libraries. Common reasons to modify a netlist include:

-

Special characters

-

Pin number changes

-

Redundant net names

It is important to document any changes you make to a netlist file. If you encounter an error during integration, it’s worth checking whether there are any special character violations, pin number mismatches, or redundant net names that need to be addressed before you can start designing your layout.

Now that you know what a PCB netlist is, you can avoid format violations by sticking to the same EDA software ecosystem. OrCAD X Capture integrates seamlessly with both OrCAD X PCB Editor, Presto PCB Editor and the more comprehensive Cadence Allegro X PCB layout tool. Check out Cadence’s suite of PCB design and analysis tools today.

Leading electronics providers rely on Cadence products to optimize power, space, and energy needs for a wide variety of market applications. To learn more about our innovative solutions, talk to our team of experts or subscribe to our YouTube channel.