What is Thermal Design in HDI? Managing Heat in Ultra-Thin Dielectrics and Microvia-Dense Regions

Thermal design in high-density interconnect (HDI) refers to the engineering strategies used to manage and dissipate heat in densely packed printed circuit boards. Thermal management grows more challenging as electronics shrink. HDI designs concentrate more functionality, and more power dissipation, into smaller areas while using thin dielectric materials that provide limited thermal spreading. This post covers thermal design principles specific to HDI construction, from via array design to copper balancing strategies that prevent warpage while optimizing heat flow.

Designing Effective Thermal Via Arrays

Thermal vias provide conductive paths for heat to flow from hot components through the PCB to heat sinks, chassis attachment points, or simply larger copper areas that can radiate and convect heat away. In HDI designs, thermal via arrays must work within the constraints of microvia technology while meeting heat transfer requirements.

The thermal conductance of a via depends primarily on its cross-sectional area. A plated through-via with 12-mil finished diameter and 1-mil plating has a copper annulus with area of approximately 34.5 square mils. A filled 4-mil microvia has a solid copper cross-section of only 12.6 square mils, about one-third the area.

To match the thermal performance of a through-via array, a microvia thermal array needs significantly more vias. Where ten through-vias might suffice, thirty or more microvias may be required for equivalent heat transfer. The benefit is that microvias, being smaller, can pack more densely, but designers must explicitly calculate thermal via count rather than simply matching the pattern of a through-via reference design.

For components with high thermal dissipation, a hybrid approach often works best: microvias in signal-dense regions where their small size enables routing coexistence, with through-vias or large buried vias in dedicated thermal zones where signal routing isn't required.

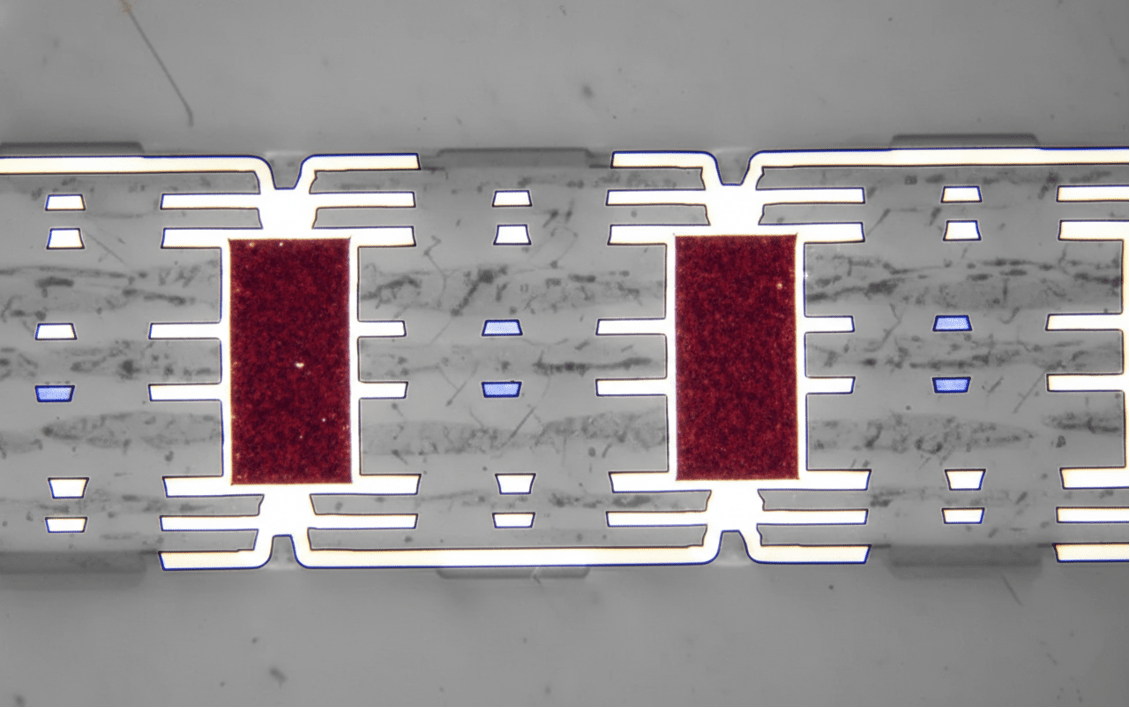

Figure 1: Cross-section photograph of a thermal via array

Heat Spreading in Thin Dielectric Cores

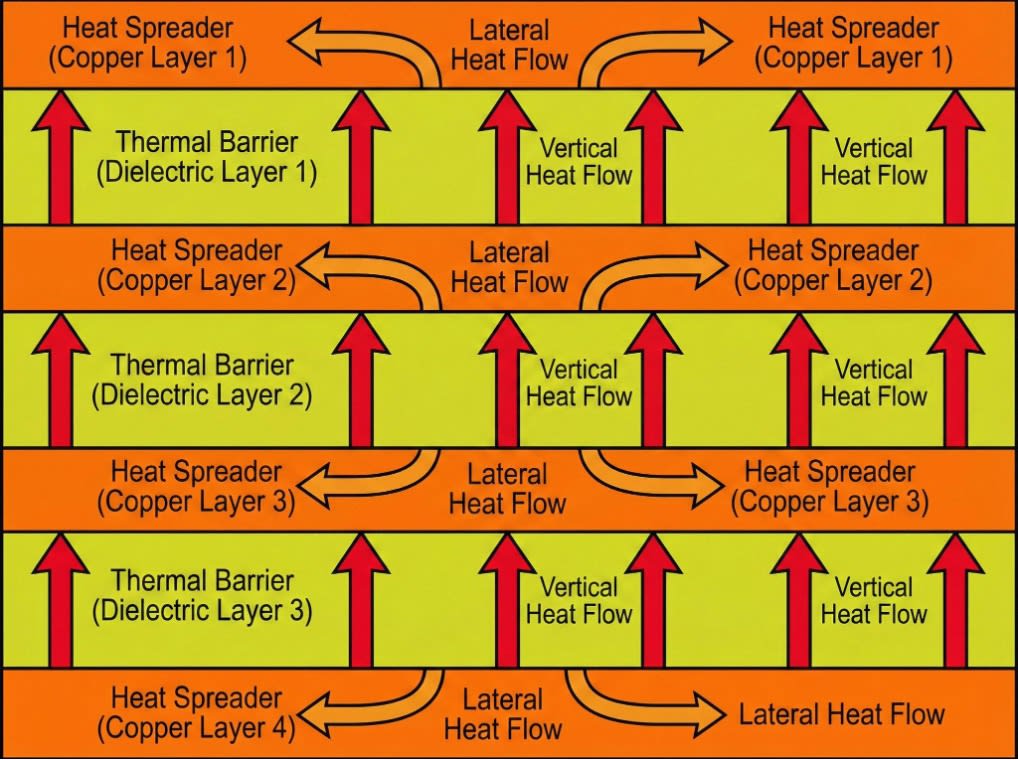

Heat flows through PCBs by two mechanisms: conduction through copper, which is highly efficient, and conduction through dielectric, which is highly inefficient. The thermal conductivity of copper is approximately 385 W/m·K; FR-4 dielectric is around 0.3 W/m·K. This massive ratio of 1000:1 means heat spreading occurs almost entirely within the copper layers.

Dielectric layers act as thermal barriers that heat must traverse vertically to reach the next copper spreading plane. Thinner dielectrics reduce this barrier, improving vertical heat transfer, but at the cost of concentrated heat intensity at each copper layer.

HDI stackups with 2-3 mil buildup dielectrics transfer heat vertically more efficiently than conventional 4-5 mil dielectrics, but each copper layer beneath a hot component sees more intense thermal loading. This concentration can push copper and dielectric temperatures higher locally even as overall thermal resistance decreases.

Effective thermal design in thin-dielectric HDI requires adequate copper area on each plane layer to spread the heat conducted from above before passing it to the next layer. Ground planes that serve as references for high-speed signals also serve as heat spreaders, a fortunate alignment of purposes. But power planes with splits or cutouts may not spread heat uniformly; thermal analysis should verify that plane patterns provide adequate spreading in thermally critical regions.

Figure 2: A stackup cross-section diagram showing heat flow paths through an HDI stackup.

Calculating Microvia Current Capacity Limits

Optimize your HDI PCB designs with insights into current flow, power delivery, and voltage stability.

Microvias carry DC and AC current just like traces, and their small diameter limits current capacity. The IPC-2152 standard provides guidance on current capacity for traces, but microvia capacity requires additional consideration of the three-dimensional current flow pattern and the thermal environment within the via structure.

A conservative rule of thumb for filled copper microvias: peak current capacity of approximately 0.5A per mil of via diameter. A 4-mil microvia might safely carry 2A continuous; a 6-mil microvia might handle 3A. These values assume reasonable ambient conditions and moderate overall board heating.

For power delivery applications requiring higher current, multiple paralleled microvias or larger-diameter vias (or via types) are necessary. The capacitance and inductance benefits of microvia PDN design must be balanced against the current capacity requirements of the power rail being implemented.

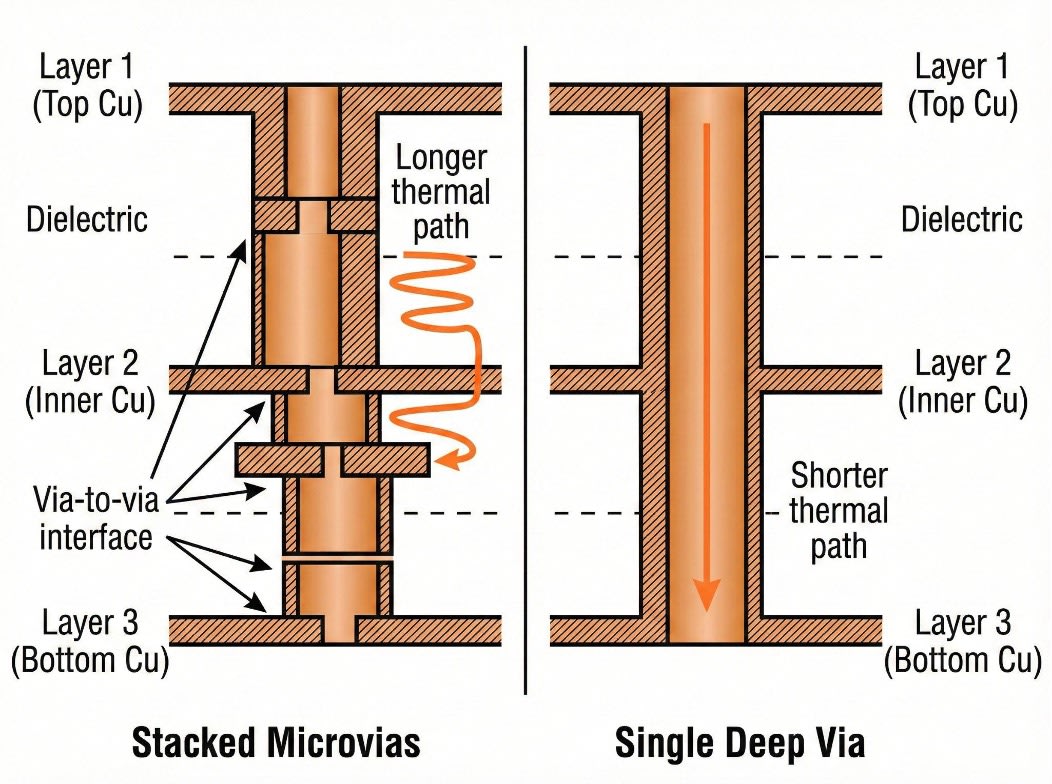

Note that stacked microvias don't have the same current capacity as a single deep via of equivalent depth. Each via-to-via interface adds a small resistance contribution, and heat generated in the middle of a stack has a longer thermal path to reach cooling surfaces.

Figure 3: Stacked microvias vs. a single deep via, with labels highlighting the via-to-via interfaces and the longer thermal path in the stacked configuration.

Copper Balancing to Prevent PCB Warpage

Warpage is the bowing or twisting of the PCB during manufacturing or operation. It results from unbalanced stress states within the board structure. Copper and dielectric expand at different rates under heat. When copper distribution is uneven, differential expansion creates internal stresses that deform the board.

HDI designs face elevated warpage risk due to asymmetric copper distribution. This often comes from dense signal routing beneath components on one surface (often top-heavy), sequential lamination that can lock in residual stress from each cycle, and thin overall board construction that provides less mechanical stiffness to resist bowing.

Copper balancing strategies include:

- Adding copper thieving (dummy fills) in sparse regions to match copper density with dense regions.

- Maintaining symmetric copper percentage between corresponding layer pairs (layer 1 vs. layer N, layer 2 vs. layer N-1).

- Avoiding large copper pours on one side of the board without corresponding copper on the other side.

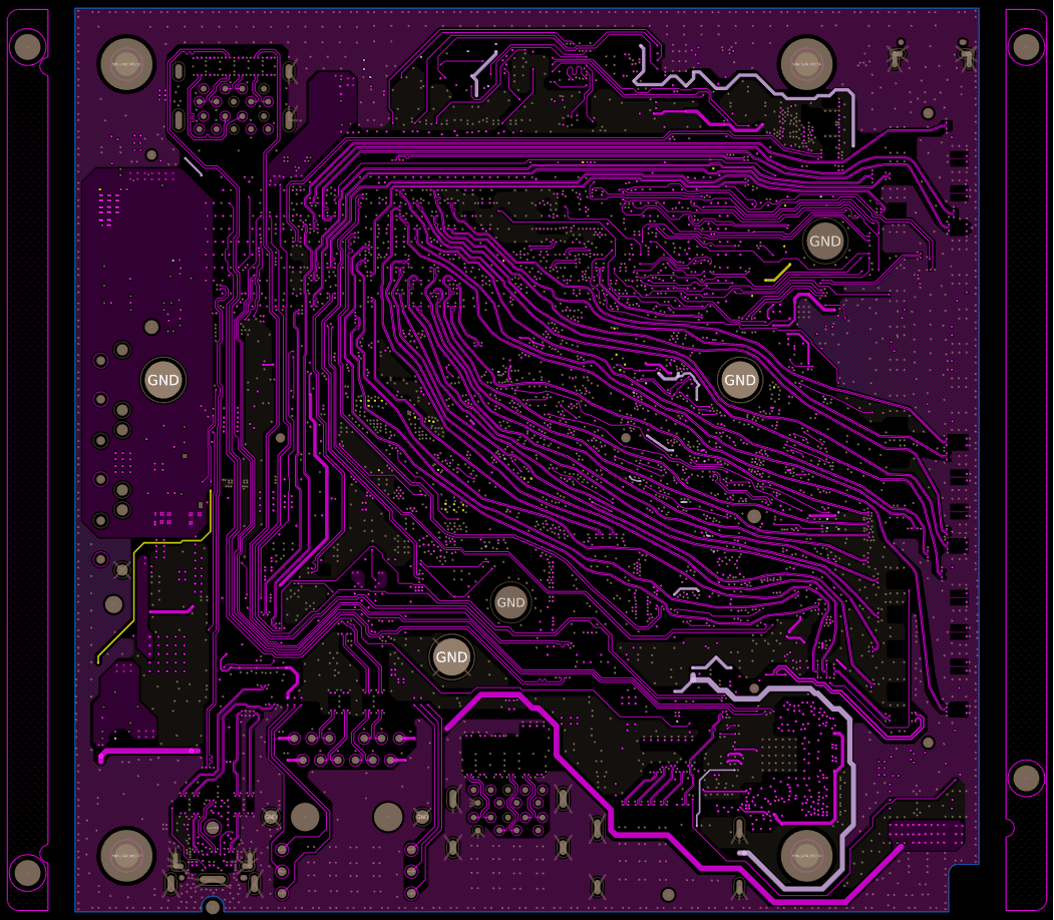

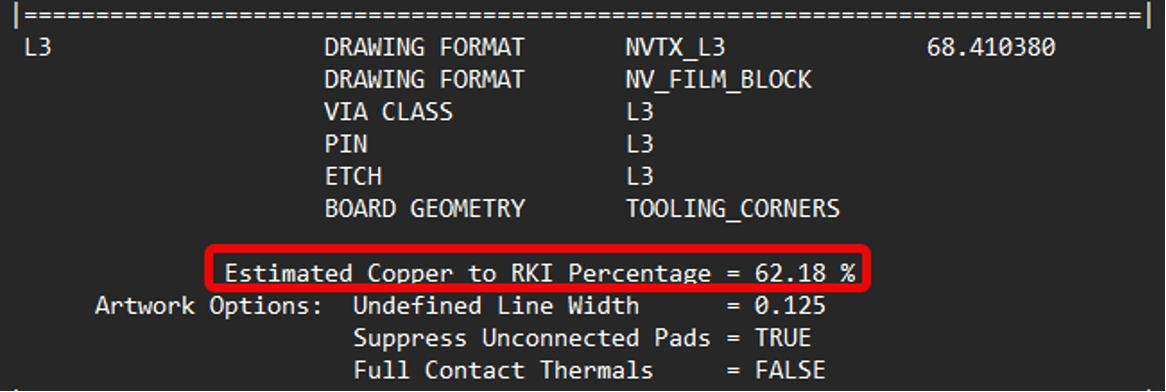

Most major EDA tools include copper balance analysis features that display copper percentage by layer and by region. Run this analysis iteratively during layout and adjust fills to maintain balance. Target copper percentage variation below 10-15% between corresponding layers.

Figure 4: A screenshot or example of a copper balance analysis report from Allegro X PCB Layout showing copper percentage on layer 3 of the NVIDIA Jetson AGX Orin 64 GB - total copper area/route keep-in (RKI) = 62.18% (healthy balance).

When to Combine HDI with Metal-Core or Hybrid Stacks

Some applications demand thermal performance beyond what standard FR-4 HDI can provide. Metal-core PCBs (MCPCB) incorporate an aluminum or copper core layer that dramatically improves in-plane thermal spreading and provides a direct thermal path to heat sinks.

Hybrid HDI-MCPCB constructions place HDI buildup layers over a metal core, providing both the routing density of HDI and the thermal performance of metal-core construction. These designs are common in LED lighting (where high-power LEDs require efficient heat extraction) and in power electronics (where switching devices generate concentrated heat).

Considerations for hybrid construction include CTE mismatch between metal core and dielectric (aluminum CTE ~23 ppm/°C vs. FR-4's in-plane CTE of ~14-18 ppm/°C), via isolation requirements where vias pass through or are adjacent to the metal core, and limited fabricator capability, as not all HDI fabricators offer metal-core hybrid construction.

Alternative thermal enhancement approaches include embedded coin technology (thick copper slugs pressed into the PCB beneath hot components), heavy copper layers (2-4 oz copper vs. standard 1 oz) on planes serving as heat spreaders, and ceramic-filled dielectrics with improved thermal conductivity.

The right thermal enhancement approach depends on power dissipation level, form factor constraints, cost sensitivity, and required reliability. Engage thermal analysis early in the design process to establish requirements before committing to a stackup architecture.