PCB Clearance and Spacing Rules in OrCAD X Presto PCB Editor

Key Takeaways

-

PCB clearances establish the minimum distance necessary for fabrication or to dissuade coupling for in-circuit performance.

-

Typically, the BGA (or the tightest pitch component) dictates the minimum clearance, but clearance can vary across the board to enhance yield.

-

Clearance can also extend to the board's 3D model to prevent collisions in complex flex and rigid-flex assemblies.

PCB clearance establishes the minimum distance between board objects to prevent shorts, EMI, and manufacturing errors.

Clearance is an essential aspect of any electronic device’s reliability. In extreme cases, intersecting nets cause shorts, leading to aberrant runtime behavior and potential component or board damage. However, induced current can also affect nearby traces/components (i.e., electromagnetic interference or EMI); designers must consider the proximity between high-speed nets and their susceptible surroundings. Finally, PCB clearance also comes into play when considering the precision of fabrication, assembly, and testing/rework technologies to avoid impacting yield and aid prototyping efforts.

OrCAD X Presto PCB Editor PCB Clearance Options

|

Clearance Scope |

Clearance Objects |

|

|

How PCB Clearance Impacts Performance

Historically, clearance has recently developed in electronic quality and reliability, mainly owing to the rapid rise (no pun intended) of digital signal logic transitions. Clearance is closely related to creepage: the former represents the air gap between conductive surfaces (i.e., as the crow flies), while the latter is the surface path linking conductive surfaces. Typically, clearance can be shorter than creepage because air acts as a reasonably high dielectric (up to 3 kV/mm). Note that conductive surfaces extending past the pad may cause the clearance between two surfaces to be shorter than the creepage; otherwise, the clearance is greater than the creepage.

More insidious than arcing from dielectric breakdown is the potential for undue interference via induction – high current (or rapid changes in current) creates a magnetic field centered around a trace. Nearby traces experience a proportion of this magnetic field based on their distance from the originating trace and the strength of the current or current change. Since the current or current change carried by a trace typically reflects some functionality of the design intent, it’s more straightforward to provide ample spacing between nearby traces to reduce the strength of the coupling. Of course, ample spacing will depend on the design. A good rule of thumb is 3W and 5H:

- Measured center to center, traces should be no closer than three widths in the plane.

- Traces should be no closer than five heights of the distance from a trace to its nearest reference plane for minimal broadside coupling (coupling between overlapping traces across layers of the stackup). Additionally, designers can use a cross-hatch routing method on neighboring signal layers to minimize the coupling potential.

Customizing Clearance Rules

With high-density interconnect (HDI) designs, these rules (specifically, 3W) may not be feasible when attempting to wring out as much routable area as possible from the board. In these cases, clearance rules can greatly avail the designer by offering global and local checks for spacing that confirm manufacturability and performance. Setting up clearance rules in OrCAD X Presto PCB Editor is straightforward:

-

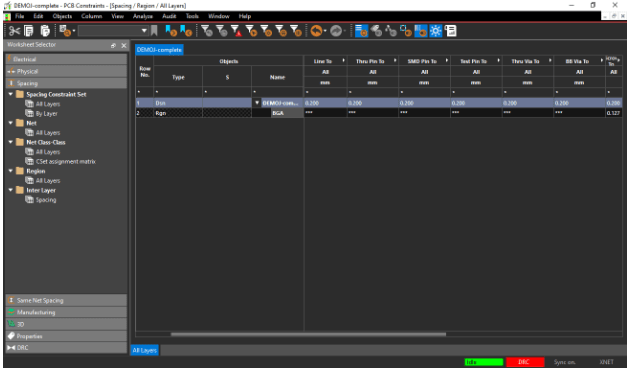

In the top navbar, navigate to Tools > Constraint Manager.

-

In the Worksheet Selector submenu, expand Spacing.

-

Users have several options to customize their clearance rules:

-

Under the Spacing Constraint Set, users can define global clearance values by object type and individual layer.

-

Under Nets, users can define object clearance values according to net names.

-

Under Net Class-Class, users can define object clearance values grouped by Net Classes.

-

Under Region, users can define object clearance values within defined layout areas.

-

Under Inter Layer, users can define object clearance values between layers.

-

-

For Same Net Spacing, users can define clearance for same-net objects. Objects of the same net will not flag a violation without same-net spacing rules since no short is detected. Same-net collisions can be an issue when the DRC doesn’t recognize certain object types (e.g., overlapping vias) as a manufacturability concern. Users can set same-net spacing rules globally, by layer, net, and region.

-

Lastly, the 3D worksheet allows designers to check for clearance between 3D objects such as components, the board edge, and rigid-flex sub-assemblies.

Clearance depends on the manufacturer's precision and the final product's desired quality. For designers, it’s worthwhile to start at the point of highest constraint: the smallest pitch of the layout. The clearance here represents the absolute minimum clearance value board-wide, and for cost efficiency, designers can restrict the most exacting clearance until breakout. The clearance is almost always tightest in the high-pin density packages (BGAs, occasionally LGAs); designers should develop the clearance from this pin pitch and consult with their manufacturer to determine whether the pitch is acceptable for their yield quota. As mentioned, designers can define the tightest clearance locally when necessary and relax the ruleset elsewhere for better manufacturing quality.

Cadence Solutions for Performance and Manufacturability

PCB clearance establishes the minimum spacing between objects of different and the same nets; the former counters electromagnetic interference caused by coupling, while the latter prevents manufacturing errors from overlapping board features. The exact PCB clearance will depend on the minimum breakout necessary for the tightest pitch component(s) on the board; to tamp down on per-board costs, designers may wish to relax the tightest clearance outside of the board areas where it’s necessary. Clearance is one of the many violations designers will want to check for but the new OrCAD X platform doesn’t stop there: the Constraint Manager supports broad flexibility for custom rulesets. Interested in learning more? Check out the Cadence PCB Design and Analysis Software page for a full range of modern PCB design, testing, and simulation solutions.

Leading electronics providers rely on Cadence products to optimize power, space, and energy needs for a wide variety of market applications. To learn more about our innovative solutions, talk to our team of experts or subscribe to our YouTube channel.