Power Grid Design in VLSI: Challenges, Techniques, and Optimization

Key Takeaways

-

Power grid design involves distributing VDD and VSS uniformly to prevent IR drop and ensure each transistor receives the correct voltage.

-

IR drop, ground bounce, and electromigration can lead to slower device response, noise, and power grid degradation.

-

Use wider metal paths, decoupling capacitors, and efficient thermal management to improve power distribution and chip reliability.

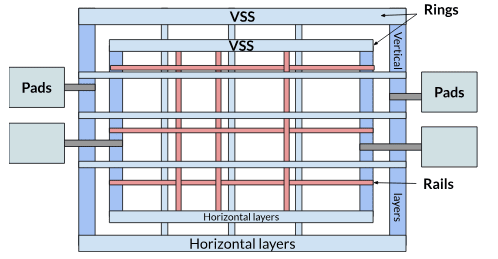

Power grid VLSI diagram.

A power grid is a network of conductive pathways that connect a power source to each component in a circuit. The grid must be designed to deliver power at a sufficient level to prevent issues like component failure or reduced operational speed. Power planning, a component of the floor planning phase in physical design, involves routing VDD and VSS paths—often in a mesh configuration—to uniformly distribute power and minimize IR-drop caused by metal resistance. The power grid serves as the backbone, supplying the necessary voltage and current across the chip, ensuring each transistor functions as expected. Additionally, it mitigates risks like electromigration, thermal issues, and voltage drops, which can critically affect the reliability of the chip-

Generally, adjustments are made to the width of the VDD/VSS paths in different areas of the design based on their power needs. Specifically, the paths are made wider to decrease resistance and ensure robustness. This process can be manually controlled or automated using an EDA tool. Read on as we discuss power grid design for VLSI (very large scale integration).

Power Grid Design for VLSI Challenges and Mitigation Techniques

|

Challenge |

Description |

Impact |

Mitigation Techniques |

|

IR Drop (Voltage Drop) |

Voltage reduction occurs in the power supply network due to resistance in the power lines. Can be static or dynamic. |

Lower operating voltage can lead to slower device response and potential operational failure. |

Use thicker metal layers with lower resistance; optimize power grid design to reduce resistance; add decoupling capacitors. |

|

Ground Bounce and L di/dt Noise |

Fluctuations in ground potential due to large current draws from nearby circuits switching simultaneously. |

Can lead to noise and instability, affecting the reliability of signal transmission. |

Use decoupling capacitors to stabilize ground voltage; ensure even power distribution to reduce local current spikes. Design with lower inductance in power distribution lines; |

|

Electromigration |

Gradual displacement of metal atoms due to high current densities, degrading the metal lines over time. |

Can lead to broken connections in the power grid, reducing the reliability and lifespan of the chip. |

Use higher metal layers with better resistance to electromigration; carefully manage current density across the power grid-. |

|

Heat Dissipation |

As power density increases with smaller chip sizes, heat buildup becomes a challenge, leading to hot spots on the chip. |

Can damage the chip or reduce its lifespan if not properly managed. |

Incorporate efficient thermal management techniques; distribute power evenly to prevent localized overheating. |

|

Power Grid Simulation Complexity |

Simulating power grids, especially large VLSI designs, can be computationally intensive and time-consuming. |

Difficulties in generating accurate simulations and identifying worst-case scenarios for voltage drops. |

Automate stimulus generation and worst-case scenario identification; use fast simulation algorithms to manage large designs efficiently. |

|

Decoupling Capacitor Placement |

Incorrect placement of decoupling capacitors can lead to either ineffective power smoothing or unnecessary power consumption. |

Can increase static power consumption and waste silicon area without resolving the voltage drop issues. |

Strategic placement of capacitors in critical regions identified through simulation-. |

|

Power Density |

Higher transistor counts and smaller form factors lead to increased power density, which can strain the power grid. |

Leads to more significant heat generation and potential reliability issues due to voltage fluctuations. |

Optimize power grid design, increase the number of power pins, and ensure adequate power distribution throughout the chip. |

|

Design-Time Predictability |

The increasing complexity of power grids makes it difficult to predict performance during the design phase. |

Can lead to failures during chip operation due to unforeseen power-related issues. |

Early-stage simulations and iterative verification to improve predictability; utilize advanced simulation tools. |

Power Grid Design Basics

Power grid design in VLSI is centered around creating a network of metal lines that distribute power across the chip efficiently. These lines are power and ground delivery networks and must be made with minimal resistance for optimal current flow. A well-structured power grid is essential for minimizing voltage drops and reducing the risk of hot spots, where concentrated power consumption could lead to overheating. The design process typically involves placing thin metal lines throughout the chip and connecting them to external power sources via power pads.

The power grid design process follows several steps:

-

Design Definition: Engineers define the structure of the grid based on the chip layout and overall power needs.

-

Power Grid Simulation: Simulations are run to analyze power distribution, identify potential voltage drops, and locate hot spots.

-

Optimization: Based on the simulation results, the power grid is optimized. This may involve adding additional metal lines or decoupling capacitors to smooth voltage fluctuations.

Power Grid Verification Techniques

In VLSI design, after the power grid is laid out, it is verified to ensure it meets performance and reliability standards. Power grid verification often involves complex simulations that assess how the grid handles IR drop, ground bounce, and L di/dt noise. The simulations take into account:

-

the various current loads,

-

toggle rates,

-

and spatial constraints,

to ensure the grid can handle all operational scenarios without failure. Automatic stimulus generation and careful selection of worst-case scenarios are vital for comprehensive verification.

Basics of Power Planning

The architecture of power distribution includes several levels:

-

Power Pads: Entry points for power into the chip.

-

Power Rings: Surround the chip, carrying VDD and VSS.

-

Power Stripes: Extend from the rings across the chip, also carrying VDD and VSS.

-

Power Rails: Link the VDD and VSS directly to the standard cells.

The layout process includes the placement of the core power ring, vertical and horizontal power straps within the core, and connections for standard cells, block power, and I/O power. Initially, power dissipation is estimated using tools or calculations, which then guide the design parameters like the widths of power rings and straps and the number of vertical and horizontal straps needed.

Vertical and horizontal straps distribute power throughout the core area to macros and standard cells. Finally, connections between the macro and standard cells pins to the straps and power and ground rails are established to complete the power distribution network.

Power Grid Design Step-By-Step Summary

|

Power Planning Element |

Description |

|

Power Grid Definition |

A network of metal lines that distributes power (VDD) and ground (VSS) across the chip. Power pads serve as entry/exit points for current, and the layout is based on chip design and power requirements to ensure even power distribution. |

|

Voltage and Current Requirements |

Understanding the voltage and current needs of different chip blocks. Ensuring robust power delivery to high-performance blocks by using wider metal lines with lower resistance to minimize IR drops. |

|

Decoupling Capacitors |

Strategically placed capacitors that smooth voltage fluctuations and provide short bursts of power during high-demand periods, ensuring stable voltage supply to critical components. |

|

Simulating Power Distribution |

Running simulations to analyze power flow and identify issues like voltage drops or hot spots. Adjustments are made to optimize power delivery and ensure the grid can handle dynamic changes. |

|

Electromigration and Power Integrity |

Ensuring metal lines can handle high current densities to avoid electromigration. Maintaining power integrity by preventing noise, voltage drops, and fluctuations that can disrupt chip performance. |

|

Power Grid Optimization |

Based on simulation results, the power grid can be optimized by adding more metal lines in critical areas or increasing the width of existing lines to reduce resistance and minimize voltage drops. |

|

Thermal Management |

Ensuring that power planning accounts for heat dissipation to prevent hot spots and thermal damage. Proper power distribution and integration of thermal management techniques help maintain optimal chip temperature. |

|

Power Gating and Clock Gating |

Techniques to conserve power by shutting down or stopping the clock signal to unused sections of the chip during idle periods. This significantly reduces power consumption during low-activity periods. |

|

Dynamic Voltage and Frequency Scaling (DVFS) |

Adjusting the chip's voltage and clock frequency based on workload to balance performance and power consumption. Higher voltage for demanding tasks and lower voltage for simpler tasks help conserve power. |

Once you’ve learned about power grid design for VLSI, and are ready to package your IC, look no further than Allegro X Advanced Package Designer. Allegro X Advanced Package Designer provides everything you need in one platform for package design, enabling seamless workflow efficiency and reliable power distribution across your chip. Discover Allegro X Advanced Package Designer to streamline your design process today!

Leading electronics providers rely on Cadence products to optimize power, space, and energy needs for a wide variety of market applications. To learn more about our innovative solutions, talk to our team of experts or subscribe to our YouTube channel.