Utilizing SPICE Simulation to Extract Parasitic Resistance, Inductance, and Capacitance

Key Takeaways

-

Parasitics cause a system to behave contrary to its ideal behavior, causing deviations in equivalent impedance, bandwidth, dispersion, and other important quantities.

-

Parasitics arise due to the arrangement of conductors and other elements in a PCB layout, which produces complex frequency-dependent signal and power behavior.

-

Front-end SPICE simulators can be used to estimate parasitics by using regression to model data, but accurate extraction requires a field solver in a real PCB layout.

Each of these traces will be affected by parasitics and signal coupling, which will have major influences on signal behavior in the PCB layout.

Many designers are used to thinking about system behavior in terms of circuit models. These models and circuit diagrams are correct up to a point, but they lack some important information that determines the behavior of your system. The information that is missing from a circuit diagram is the geometry of a real PCB layout, which determines how elements in a system electrically and magnetically couple with each other.

So what causes electromagnetic field coupling between circuit elements, conductors, ferrites, and other complex structures in a real PCB or IC? This is governed by the interaction between the electromagnetic field and matter, but a conceptual way to summarize signal behavior in a complex system is to think of coupling in terms of parasitic circuit elements, or simply, parasitics. Bringing parasitics into a circuit model helps you explain unintended or undesired signal and power behavior in a real system, making parasitic modeling tools very helpful for understanding circuit and product behavior.

Coupling between different structures in your PCB can be modeled with circuit diagrams in a SPICE simulator as well as with broadband SPICE models. Although you can’t extract parasitics directly, you can determine the behavior of parasitics in circuit diagrams, and you can extract parasitics from test and measurement data from real circuits. Read on to understand the role played by SPICE simulators in extracting parasitic circuit elements.

How to Extract Parasitics with SPICE

As mentioned above, you cannot directly extract parasitics from a PCB layout using a SPICE simulator. This is because circuit diagrams simply cannot account for some important features of a real PCB, IC, or any other electrical system. Parasitics are represented in a circuit diagram as resistors, capacitors, and inductors, depending on their behavior in the frequency domain. Note that parasitics are almost exclusively discussed in terms of LTI circuits, meaning the parasitics are also treated as being linear and time-invariant. Time-variant and nonlinear parasitics take more sophisticated modeling techniques involving manual iteration in the time domain. They can also be very sensitive to initial conditions in the system, especially in the presence of feedback.

Although a real PCB is complex, LTI systems encompass the vast majority of practical electrical systems. Determining the effects of parasitics is really about determining the frequency behavior of a system because the effect a parasitic element has on a signal is a function of frequency. By comparing the frequency behavior of the [ideal system + possible parasitics] with [real system measurements], you can determine the possible parasitics that produce frequency-dependent behavior in your system.

What Determines Parasitics, and What Isn’t Considered in Your Circuit Diagram?

There are many aspects of a real system that create unintended parasitics in a PCB layout, IC, or any other electrical system. It’s important to note what can’t be considered in a circuit diagram before trying to use a SPICE simulation to extract parasitics.

-

Geometry. The distance between various conductors, their arrangement on a board, and their cross-sectional area will determine DC resistance, parasitic capacitance, and parasitic inductance.

-

Dielectric constant. PCB dielectrics have a high dielectric constant, which determines the parasitic capacitance between circuit elements.

-

Magnetic permeability. For magnetic components, the magnetic permeability also plays a role in determining signal and power behavior as these components create parasitic inductance. Ferrite transformers and other magnetic components can act like inductors or radiators when operating at high frequencies.

-

Traveling wave behavior. Any signal propagating in a real PCB and interconnects is a propagating waveform. The propagation of electromagnetic waves produces transmission line effects in interconnects, which cannot be modeled with a simple circuit diagram. Your SPICE simulation needs to be modified to account for the finite velocity of the waveform.

Things like fiber weave effects specifically within the PCB substrate cannot be easily simulated with a circuit model or post-layout simulation as the circuit models involved can become intractable. However, circuit simulations can help you broadly examine frequency-dependent behavior in your PCB. Other parasitics, such as input/output capacitance on an integrated circuit, or bond-wire inductance, can be easily determined because the type of parasitics and where they are located is known with certainty.

The example schematic below shows a typical circuit model used to examine and explain ground bounce in an integrated circuit. This effect arises due to parasitic inductance in the ground lead (marked L in the schematic). However, there are other effects in the circuit that contribute to circuit behavior in the presence of ground bounce. The two capacitors at the driver output and load input model parasitic capacitance due to pins on integrated circuits. The resistor on the I/O line models its parasitic DC resistance.

Schematic created in OrCAD Capture CIS for modeling ground bounce due to parasitic inductance. Other parasitics are placed in this schematic for modeling.

Methods for Extracting Parasitics with SPICE

The goal in parasitic extraction is often to get an estimate of the frequency-dependent behavior of a system, so as to broadly characterize the system as capacitive or inductive in certain frequency ranges. With the type of schematic shown above, you can extract parasitics by comparing your simulation results with experimental measurements (see Method 2 below). Simply simulate the circuit with a frequency sweep or source the circuit with an impulse for transient analysis. You’ll then need to compare the results with your measured data to determine the parasitics in your system.

There are two ways to extract parasitics in SPICE. Both of these require some knowledge of possible parasitics in the system or a comparison with measurements from a finished PCB layout:

-

Analytical methods. This involves calculating the frequency-dependent behavior of trivial or nontrivial circuit models using analytical equations. Component values are typically assumed from datasheets or prior experience.

-

Regression methods. This is used when the equivalent value of a parasitic circuit element is unknown, although a general model that describes the relationship between the parasitic and your measurements is known. Standard regression methods can be used to determine consistency between your model and data.

In the forthcoming example, we’ll consider how to run a PSpice simulation required for both methods. Rather than assume single values for various parasitics, we’ll sweep through a range of possible values and examine the frequency response with a SPICE simulation. The results could be used to build a model describing how the frequency response of the circuit depends on a particular parasitic value, which can then be used to calculate the value of a parasitic from measured data.

Example: Capacitor Self-Resonance Frequency

As an example, let’s look at how to extract the parasitics in a capacitor by identifying its self-resonance frequency. Self-resonance is a well-known phenomenon in capacitors at high frequency and occurs due to parasitic series resistance and inductance. In the schematic below, we have a capacitor rated at 4.7 pF and we want to extract the parasitic inductance and resistance.

Schematic created in OrCAD Capture CIS for modeling capacitor self-resonance due to ESR and ESL.

Here, we want to sweep the frequency of the source while also sweeping the value of the parasitics. This is done with a parametric sweep in the frequency domain, which will give a set of curves for our current measurements; these could then be used to extract the self-resonance frequency and the ESL value. To do this, you need to set up a global parameter for each component value you want to sweep. This is done by adding the PARAM part to the schematic, and then by entering the parameter name into the component value.

The set of curves below shows results obtained when sweeping the inductor value from 1 nH to 100 nH. The current supplied by the source is plotted on the y-axis. Once this data is obtained, it can be compared with measured data to determine the true value of the capacitor’s parasitic inductance.

Self-resonance curves for the capacitor in the above schematic.

You can use the same procedure with a resistance sweep to determine the true value of ESR. As an example, going back to the ground bounce diagram, you could sweep the parasitic capacitance values and compare the results with your measured signal (e.g., on an oscilloscope trace).

The data extracted from the SPICE simulation can be used in either an analytical method or a regression method. In the analytical method, as long as a model for the frequency response as a function of parasitic value exists (in this case, capacitor self-resonance frequency), you can directly calculate the parasitic from your simulated response. In the above example, we would want to compare a measured impedance or self-resonance with the simulated values to determine the exact value of the parasitics.

If you have a simulated curve that closely resembles your measured curve, then you know your model explains the behavior of your circuit with high precision. In practice, you won’t have such a clean match, so you’ll have to fit your simulated data (in this case, self-resonance frequency) to a model (usually linear or power law). You can then plug your observation from your measured data into the model to calculate the value of the relevant parasitic. Similar techniques can be used in other tests and contexts.

When to Go Back to Your Layout

At some point, real PCB layouts become so complex that trying to extract parasitics by fitting to an equivalent circuit model becomes intractable. Technically, you could write a program that would do repeated fitting between data and some predefined trial models, but your program will still have to guess exactly what parasitics and their equivalent circuit arrangement (parallel, series, or nontrivial) are producing your signal behavior. At this point, the alternative is to go back to a field solver to extract parasitics from your PCB layout.

Extracting parasitics in a post-layout view is quite simple. Just select the interconnects you want to analyze and run the automated extraction tool. The integrated field solver will calculate equivalent parasitics in your PCB layout directly from Maxwell’s equations. You won’t need to use regression to fit a circuit model to examine PDN impedance, trace impedance, mutual coupling, and other factors that impact signal behavior. An example showing coupling strength plotted as a heat map in a PCB layout is shown below.

Parasitics are used to determine coupling between nearby traces, which can be quantified using a coupling coefficient.

In the above image, the “coupling coefficient” is a lumped capacitive and inductive coupling coefficient, which can be a complex function of frequency. In other words, the coupling coefficient is determined at a particular frequency or bandwidth; you don’t need to manually extract capacitive and inductive parasitics to determine signal behavior.

Parasitics are useful in understanding circuit behavior in many systems, such as large antennas and lower-speed signals. High-speed and high-frequency designs go a bit further than looking at parasitics when analyzing signal behavior in a PCB layout. Instead, you need to create S-parameter models for PCB structures using a full-wave 3D EM field solver. The best extraction tool will convert your extracted S-parameters back into broadband SPICE models, which can then be used in circuit simulations.

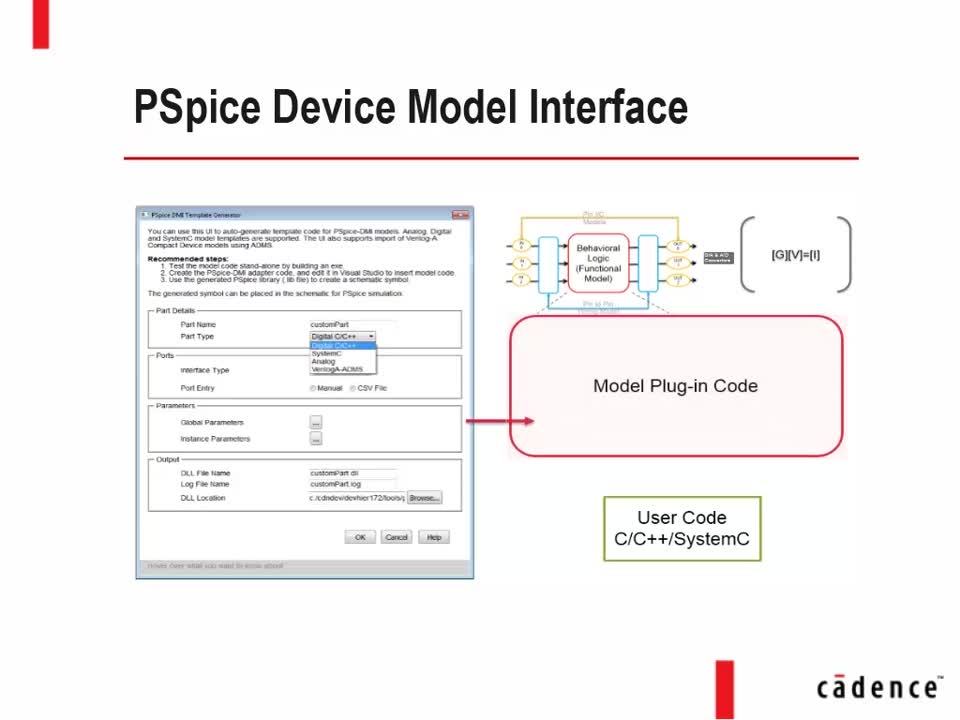

The parametric analysis and model editing tools in PSpice let you build models and perform parametric simulations that help you extract parasitics from circuit models. When you need to work in your PCB layout, you need the hybrid simulation features in Sigrity SI Extraction, which show you parasitics directly from post-layout simulation data. You can also examine signal behavior directly with Sigrity Advanced SI, which allows reflections, coupling, impedance, and return paths to be simulated in your layout.

If you’re looking to learn more about how Cadence has the solution for you, talk to us and our team of experts.