ICT vs Flying Probe: Factory Testing of PCB Assemblies

Factory testing comes in numerous flavors. The goal is to ship products that work in the field. Failures eat into gross margins which in turn affect the perception of the company in the market. Good customer relationships depend on timely delivery of products that meet the requirements which is the definition of quality. The IPC-650 TEST METHODS MANUAL covers the test procedures in detail.

This article will cover the following topics:

- Disposition of defective materials

- Statistical Process Control

- Stress testing Power Delivery Networks

- Bed of Nails and Flying Probe test fixtures

Inspection Prior to Release To The Factory Floor

We’re finally in the factory where units are coming off the line in rapid succession. There will be testing but there may not always be resources for troubleshooting. Rejected units can get recycled or repurposed after the more expensive components are removed. This will depend on the industry involved as well as the component mix.

When something fails, it may be sent to a caged area of the factory known as MRB or Material Review Board where it will sit until the next MRB meeting. They will typically meet once a week but could be brought in on a critical part the same day it’s flagged for MRB. There will be Quality Engineers, Manufacturing Engineers, Planners and others who will make a disposition whether to Use As Is, (UAI) Return To Vendor (RTV), rework, or scrap.

Test Coupons and Solder Samples

We may include impedance coupons and solder samples. The impedance coupons will have specific lengths of transmission lines similar to those that are used on the board. The measurements will be taken at frequencies that align with normal operations. The impedance range on the bare board will typically have to be within +/-10% of the specified nominal values in order to move into assembly.

In terms of the solder sample, specific tests will be run with the intention of uncovering warpage, measling, delamination and other defects that accompany the solder process. This type of instruction will be on the purchase order. The P.O. supersedes any data on the fab drawing while local and state laws have the final word on any such contract. Some stipulations on the P.O. will call for a certificate of compliance to be included. Doing an electrical test using the IPC-356 netlist is something that is commonly certified in this way.

There is a test for nearly every aspect of a printed circuit board. Warpage can be determined with a table made of granite using metal go/no-go gauges. A light table can help us see into the bare board while an xray would look at hidden solder joints of a BGA device. A piece of tape will be used to find out if the soldermask and silkscreen adhere to the board.

Statistical Process Control

The goal in manufacturing is to ship products that meet a minimum of 6 sigma quality. That is where 99.7% of the products work right out of the box. This level of quality is enough to say that the process is in control. Satellites, submarines and other stuff may call for 6 sigma quality where 99.99966% of the articles meet the requirements. The non-destructive testing may be performed on all units but more likely, a random sample is selected.

If one or more of the samples went to MRB for not meeting the acceptable quality level (AQL), then the entire lot gets rejected. The number of inspection samples for the next lot may be increased. That’s also when destructive testing of the defective samples starts. The Reliability Lab will tear down some or all of the units to find root causes and solutions.

It will probably not be economically or environmentally viable to put the whole batch into the dumpster. Instead, the units may be earmarked for a 60 day warranty rather than the usual year or two. The marginal lot would then end up with a reseller on Temu or perhaps the Dollar Store chain rather than a big box retailer.

Behavior Under Less Than Ideal Conditions

One of the key things to test aside from the physical attributes is whether the product can work over the entire gamut of acceptable voltage parameters. Every voltage domain has a minimum and a maximum input range. The standard +5V could come in as low as 4.5V and high as 5.5 Volts. The +/-10% may apply to 3.3V, 2.8V, 1.2V and so on.

One phase of the test process would have the +5V cranked up to +5.5V while all of the other voltages are set to their minimum allowable voltage. Every possible combination of acceptable min and max power is tested. The “corner cases” may seem extreme but they are emblematic of the methods used to evaluate electronics. More voltage domains equals more combinations to test.

While running at the various corners, we look at the variables that measure performance. It could be an eye diagram or a smith chart, whatever metric applies to the product. This type of stress testing will reveal any shortcomings in the power domain as well as any signal integrity concerns.

Running at high temperatures or cycling through temperatures will prematurely age electronics. A burn-in chamber will be used for this purpose. Sometimes, the product is going full-tilt until something breaks. A month-long burn-in at 80% of rated capacity is an example. If it survives that, then the “infant failures” are out of the way giving us the confidence necessary to ship the product.

Automated Testing of Printed Circuit Assemblies

Narrowing down the fault is sometimes done with In-Circuit Testing (ICT). A bed of nails is a type of fixture with spring loaded pogo pins that align with a pattern of test points on the PCB. The least costly of these uses one side of the board for probing as many connections as possible.

Figure 1. An in circuit test (ICT) fixture for simultaneous probing of both sides of the PCBA. Image Credit: Q1Test

Putting testpoints on both sides will require a clamshell fixture that is more costly. Placing the test points in close proximity to one another is also a cost driver. It’s ok to be near components with a low profile while taller components will have more generous space. Of course, larger test points are better when it comes to implementing a test fixture.

Figure 2. Nominal size and spacing for an ICT test point. Image Credit: Author

In a perfect world, the test points would be placed on a coarse grid and not clustered in a specific area. Each ICT probe will exert some force on the assembly. The result could be that the board flexes under the strain of dense test point placement.

Figure 3, Test point spacing for flying probe testing, 0,7 mm pad on 1.4mm pitch. This is a column of JTAG pins. Image Credit: Author

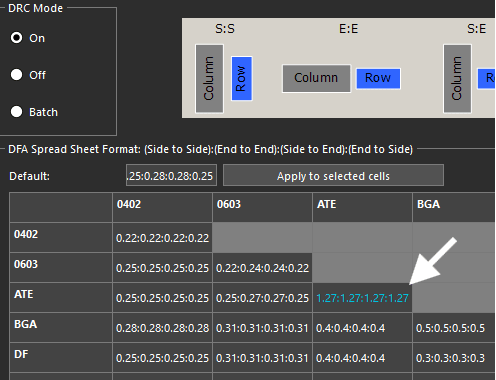

Personally, I use the Design For Assembly (DFA) tool where you can determine a part’s proximity to other parts on a case by case basis. The DFA table will have rows and columns to account for every part type. I would give the test points their own attribute where they can cozy up to the short parts, give some room to the taller ones and then put in a larger value for test point to test point spacing. That’s the trick to getting the lowest cost ICT fixture.

Figure 4. Secondary side used for flying probe ICT and select components, Image Credit: Author

Flying Probe Testing

There is an alternative to the expensive ICT fixture and that is to use a flying probe machine. It works sort of like a pick and place machine. Instead of placing parts it has multiple probe heads that “fly” around the board and take electrical measurements between pin pairs. These machines will perform better if there are a number of gratuitous test points in the power and ground planes scattered around the board.

Figure 5. An oversized courtyard at the intersection of the ATE values will single out test points for spacing rules around other test points. The category name is done at symbol level while the actual component spacing is constrained within the PCB editor. Image Credit: Author

Once they are programmed the flying head probes will run the test over and over. The time it takes will depend on how many pin pairs it has to probe. They will generally be slower in the process than a bed of nails fixture. The benefit is they are much more agile when it comes to a board revision where a few test points were moved, added or subtracted.

Figure 6. The different values in the DFA table create specific guidance in terms of spacing. The test point can be nearer to the capacitor than to another test point. Image Credit: Author

Wrapping It Up

Tests and measurements get harder with increasing component density. Competition to create the smallest, most efficient form factor drives products that are dominated by the need to do more with less. A JTAG connector may be our only access if even that. We, as the designers of embedded electronics, are pulled in several directions at once. Be flexible.