High-Speed PCB Design Guidelines

Key Takeaways

-

Preparing for high-speed PCB layout

-

Component placement and PDN development of a high-speed design

-

Some helpful PCB high-speed routing recommendations

High-speed PCB design guidelines simplify and optimize complex layouts as much as possible.

Digital circuitry is getting faster to supply the needs of today’s electronics. High-speed design used to fall into a narrow group of electronic products, but today, most products will at least have a portion of the design that can be considered “high-speed.” These designs require PCB designers to lay out their circuit boards according to high-speed rules and requirements, which is still new territory for some. To help, we have compiled some of the most common high-speed PCB design guidelines applicable to future layouts.

|

High-Speed PCB Design Guidelines: The Setup |

|

|

Schematic |

High-speed signal paths must undergo sequential layout so the designer can emulate their component placement in the PCB layout. |

|

PCB Libraries |

Librarians must check and verify the component footprints used for high-speed design. |

|

Materials and Components |

Appropriate board materials and components are necessary to avoid excessive loss from high-Dk substrates. |

|

Board Layer Stackup |

High-speed PCB designs require unbroken reference planes to help shield electromagnetic interference (EMI) and promote signal integrity. |

|

Design Rules |

A new set of design rules should be developed for a high-speed design, including differential pairs, signal paths, routing topologies, measured and matched trace lengths, and trace tuning parameters. |

Setup for High-Speed Design

Schematic

While there is a lot to set up before beginning the layout of a high-speed design, most people don’t give too much thought to the schematic. Designers should verify the parts, simulate the circuitry, and complete the design. But is the schematic itself ready to be used for layout? An unorganized schematic can create difficulty for PCB layout if the designer can’t easily understand the intent of the circuitry. High-speed signal paths, for instance, need to be laid out sequentially so that the designer can emulate their component placement in the layout. It is also helpful to highlight areas of the design for the layout team that reduce ambiguity. These include:

- Critical placement locations and which side of the board certain parts reside.

- Keepout zones around critical components.

- High-speed routing information, including routing topologies and measured/matched lengths.

- Differential pair and controlled impedance information.

PCB Libraries

As with any PCB layout, the component footprints used for high-speed design must be checked and verified, but additional library work may be necessary. For instance, some footprints used in high-frequency or RF designs may require alterations to reduce pad sizes for signal integrity. Additionally, some footprints may need a reduction to their minimum sizes to accommodate high-density design requirements. As always, component footprints should follow industry and manufacturer specifications as much as possible to comply with design for manufacturability (DFM) requirements. Many design tools, such as Cadence’s Allegro X, offer online library browsing capabilities to pull in vendor-specific footprint models.

Materials and Components

The materials used to build high-speed circuit boards merit consideration before starting the layout. Harsh operating environments may require a more robust board structure, and the physical characteristics of the materials will be needed for controlled impedance routing calculations:

-

If not communicated through the design documents, consult the electrical or signal integrity engineer to determine if the board needs high-speed materials.

-

Enhanced epoxy or PTFE materials (i.e., filled or unfilled) might be better for high-speed and high-frequency applications than “standard” FR-4s due to their lower dielectric constants, which produce less loss during signal transmission. As a rule of thumb, the faster the transmission speeds and the longer the transmission path, the more necessary high-speed materials with tight impedance tolerances become.

The PCB components must also be reviewed and confirmed by verification tools or a librarian who maintains the footprint library. With today’s supply chain problems, you must ensure you have parts available before committing to a design.

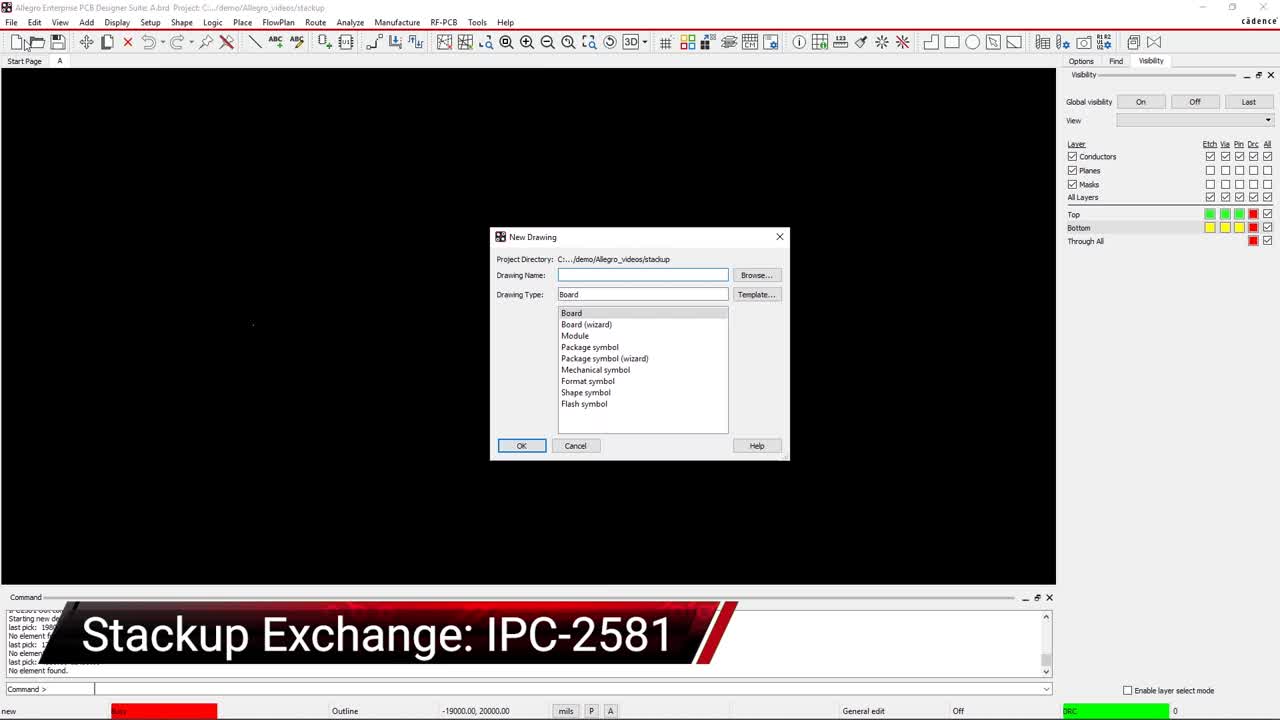

Board Layer Stackup

High-speed designs require specific stackup layers to help with EMI shielding and signal integrity; the basis of signal integrity is the shortest, direct path for the return current that minimizes the current loop and any associated inductance. The primary consideration is including a full and continuous reference plane on an internal layer that provides an uninhibited path for the return signal and establishes the correct impedance according to the impedance structure parameters outlined in the stackup/EM field solver tool. More complex board stackups will also have to account for multiple via structures that originate and terminate at different points; additionally, differences in the dielectric effect from outer layer traces surrounded on one side by air and inner layer traces surrounded on both sides by substrate will require different design constraints to achieve the same impedance values. The board layer stackup must be built into the PCB CAD database or imported from an external source; the best method is to request an IPC-2851 stackup that standardizes design data with the fabricator.

Design Rules

PCB design systems typically have a comprehensive set of design rules and constraints to set up the design. Standard circuit board designs already use component and net classes to specify spacing rules, trace widths, vias, and other constraints. With a high-speed design, a whole new set of rules should be set up for use, including:

- Differential pairs

- Routing topologies

- Controlled impedance and length-matched traces

- Delay tuning

These rules can be unique to each design or, in many cases, imported from another layout to ease the designer’s workload.

High-Speed PCB Design Guidelines for Component Placement

Component placement of a high-speed design still needs to follow the same guidelines as the placement of a standard design. The parts should be distributed evenly around the board for balance, and design for manufacturing and test rules (DFM & DFT) are crucial. This aspect includes component spacing to other parts, board features, and the board's edge. Components that run hot need additional conduction support for thermal routing, like heat sinks, thermal vias, and large copper pours to appropriately draw heat away from the source. At the same time, careful surrounding placement must not restrict the flow of air channels with nearby components. Connectors and other human interface parts should reside where users (and technicians) can easily access them.

Where high-speed design differs is the need to create the best signal integrity throughout the design. A significant portion of signal integrity depends on designing the board for clear signal return paths on the ground plane and separating digital and analog circuitry to prevent crosstalk from the much faster rise and fall times of the digital signals on the analog signals. Therefore, in addition to placing the components to support the trace routing they will need, designers must put their parts in place for clear signal returns and circuitry isolation. It is often best to floorplan the placement before arranging the actual parts on the board to accomplish intricate component placement:

- Maintain room for clear signal return paths on the reference planes.

- Allow routing channel spacing for dense data and memory bus routing.

- Avoid placing parts where analog and digital will have to wander through each other’s areas.

- Position parts to keep high-speed signal paths short and reduce trace impedance.

- Signal paths can include multiple components in the path. The schematic will often provide a sound basis for placement, but check with the manufacturer’s datasheet for more specific instructions.

3D view of some high-speed routing showing tuned traces

High-Speed Trace Routing Techniques

With a suitable arrangement of the components on the board already in place, your design will have a basic template of how the routing should proceed. However, it is essential to note that parts will likely still be moving around to refine and fine-tune the routing. Here are some PCB design guidelines for high-speed routing that can help:

-

Make sure to fully engage the design rules and constraints for line lengths, matched lengths, widths, spacing, layers, impedance-controlled routing parameters, differential pairs, trace tuning, and vias assignments.

-

Set up any necessary area rules and keep out zones as required for unique routing needs.

-

Keep routing as short and direct as possible, except for specific routing topologies and measured lengths.

-

Do NOT route over voids or breaks in the ground plane, as this risks EMI issues and impedance mismatches.

-

While routing high-speed signals, ensure they have a clear signal return path on the adjacent ground plane.

-

Give sensitive signals, such as clock lines and differential pairs, additional clearance from other routing. Three times the dielectric thickness between the signal and reference layer is often a good rule of thumb.

-

Route high-speed transmission lines on their assigned layers for return paths on the adjacent reference plane.

-

Avoid changing layers with high-speed transmission lines, but if necessary, add return path vias to keep the return current path direct and the current loop small.

-

Be cautious of high-speed transmission lines running in parallel with each other, as they may create crosstalk.

-

Also, beware of broadside crosstalk of dual stripline traces, which may have less spacing than two traces side-by-side on the same layer.

-

Wider traces reduce impedance but may not be applicable depending on design requirements.

-

To reduce inductance, minimize vias as much as possible or use blind, buried, or microvias. Backdrilling of through-hole vias can eliminate reflections that reduce signal integrity.

-

Be careful with dense areas of escape vias that block the return paths on the ground plane.

There are more high-speed PCB design guidelines than listed here, but this article provides an excellent start to the next high-speed PCB design project. In addition to the design rules and constraints already discussed (with more DesignTrue DFM rules available in Allegro X), PCB design tools have many other features that can help designers. Cadence Design and Analysis Software can help engineers find and correct design problems before building a board.